Wayne State University Dissertations

January 2020

# Tiling Optimization For Nested Loops On Gpus

Yuanzhe Li Wayne State University

Follow this and additional works at: https://digitalcommons.wayne.edu/oa\_dissertations

Part of the Computer Sciences Commons

#### **Recommended Citation**

Li, Yuanzhe, "Tiling Optimization For Nested Loops On Gpus" (2020). Wayne State University Dissertations. 2362.

https://digitalcommons.wayne.edu/oa\_dissertations/2362

This Open Access Dissertation is brought to you for free and open access by DigitalCommons@WayneState. It has been accepted for inclusion in Wayne State University Dissertations by an authorized administrator of DigitalCommons@WayneState.

### TILING OPTIMIZATION FOR NESTED LOOPS ON GPUS

by

### YUANZHE LI

### **DISSERTATION**

Submitted to the Graduate School,

of Wayne State University,

Detroit, Michigan

in partial fulfillment of the requirements

for the degree of

### **DOCTOR OF PHILOSOPHY**

MAJOR: Computer Science

Approved By:

Advisor Date

# **DEDICATION**

For my wife Jingwen, child Avery, and parents Zhiyong and Tong, and all the things that bring us joy in life.

### **ACKNOWLEDGEMENTS**

This template is a combination of work done by Mike Catanzaro and Gabe Angelini-Knoll, both formerly of the WSU math department, with some additions and synthesizations by Clayton Hayes (clayton.hayes@wayne.edu) for broader use.

This template was last update updated on 2019-03-10 by Aaron Willcock (ez9213@wayne.edu) for the updated WSU dissertation and thesis formatting guidelines. The unedited, accepted latex upon which this thesis template was most recently adapted can be found at (https://github.com/aarontwillcock/wsu-ms-cs-tufc).

## TABLE OF CONTENTS

| Dedication                                                   | ii |  |  |  |  |  |  |  |

|--------------------------------------------------------------|----|--|--|--|--|--|--|--|

| Acknowledgements                                             |    |  |  |  |  |  |  |  |

| List of Tables                                               |    |  |  |  |  |  |  |  |

| List of Figures                                              |    |  |  |  |  |  |  |  |

| Chapter 1 Introduction                                       | 1  |  |  |  |  |  |  |  |

| 1.1 Contributions                                            | 3  |  |  |  |  |  |  |  |

| 1.2 Dissertation Outline                                     | 5  |  |  |  |  |  |  |  |

| Chapter 2 Overview of NVIDIA GPUs and CUDA                   | 7  |  |  |  |  |  |  |  |

| 2.1 GPU Architecture                                         | 8  |  |  |  |  |  |  |  |

| 2.2 CUDA Terminology                                         | 10 |  |  |  |  |  |  |  |

| 2.3 GPU Properties                                           | 11 |  |  |  |  |  |  |  |

| Chapter 3 OVERVIEW OF LOOP TILING                            | 14 |  |  |  |  |  |  |  |

| 3.1 Loop Tiling on GPUs                                      | 14 |  |  |  |  |  |  |  |

| 3.2 Wavefront Parallelism                                    | 15 |  |  |  |  |  |  |  |

| 3.2.1 Square VS Non-Square                                   | 17 |  |  |  |  |  |  |  |

| Chapter 4 Related Work                                       | 19 |  |  |  |  |  |  |  |

| 4.1 Higher-Dimensional Dynamic Programming                   | 19 |  |  |  |  |  |  |  |

| 4.2 Wavefront Parallelism Optimization                       | 20 |  |  |  |  |  |  |  |

| 4.3 Time-Space Tiling for Stencil Computation                | 23 |  |  |  |  |  |  |  |

| Chapter 5 Optimizing Higher-dimensional DOACROSS Parallelism | 28 |  |  |  |  |  |  |  |

| 5.1 Introduction                                             | 28 |  |  |  |  |  |  |  |

| 5.2 Tiling-Like Data-Partitioning Scheme                     | 30 |  |  |  |  |  |  |  |

| 5.3     | Dynamic Programming in the Parallel PTAS |                                                        |    |

|---------|------------------------------------------|--------------------------------------------------------|----|

| 5.4     | 4 GPU Implementation and Analysis        |                                                        |    |

|         | 5.4.1                                    | Design and Challenges                                  | 39 |

|         | 5.4.2                                    | Two-level Fine-grained Parallelism                     | 43 |

|         | 5.4.3                                    | Analysis of the Dynamic Programming                    | 45 |

| 5.5     | Evalua                                   | ntion                                                  | 47 |

|         | 5.5.1                                    | Experimental Setup                                     | 47 |

|         | 5.5.2                                    | Analysis of Results                                    | 48 |

| 5.6     | Summ                                     | ary                                                    | 54 |

| Chapter | 6 C                                      | ptimizing Wavefront Parallelism with Non-Square Tiling | 55 |

| 6.1     | Introd                                   | uction                                                 | 56 |

| 6.2     | Proble                                   | m Statement                                            | 59 |

|         | 6.2.1                                    | Low Cache Hit Rates                                    | 59 |

|         | 6.2.2                                    | Advantages of Shared Memory                            | 60 |

|         | 6.2.3                                    | Barriers to Shared Memory Use                          | 60 |

| 6.3     | Design                                   | and Challenges                                         | 61 |

|         | 6.3.1                                    | Design Overview                                        | 62 |

|         | 6.3.2                                    | Tile Concurrency and Synchronization                   | 63 |

|         | 6.3.3                                    | Concurrency VS Data Locality                           | 66 |

|         | 6.3.4                                    | Shared Memory Efficiency                               | 67 |

|         | 6.3.5                                    | Synchronization Counter                                | 70 |

| 6.4     | Implei                                   | mentation                                              | 71 |

| 6.5     | Evalua                                   | ation                                                  | 73 |

|    |       | 6.5.1 | 1 '        | Wavefront Applications                                                          | 74  |

|----|-------|-------|------------|---------------------------------------------------------------------------------|-----|

|    |       | 6.5.2 | 2 '        | Test Cases and GPU Environment                                                  | 75  |

|    |       | 6.5.3 | 3          | Memory Subsystem Efficiency                                                     | 76  |

|    |       | 6.5.4 | 4          | Performance: Multiple Tile Sizes                                                | 79  |

|    |       | 6.5.5 | <b>5</b> ] | Performance: Cache vs Shared Memory                                             | 80  |

|    | 6.6   | Sum   | ıma        | ry                                                                              | 82  |

| Ch | apter | 7     |            | me-Skewed Tiling Optimization for High Order 2D Stencil Computa-<br>ons on GPUs | 84  |

|    | 7.1   | Intro | odu        | ction                                                                           | 84  |

|    | 7.2   | Back  | kgro       | ound and Motivation                                                             | 88  |

|    |       | 7.2.1 | 1          | Disadvantages of Different Temporal Tiling                                      | 88  |

|    |       | 7.2.2 | 2          | Difficulties of Using Existing Solutions                                        | 89  |

|    |       | 7.2.3 | 3 (        | Concurrency Modeling on GPUs for Time-Skewed Tiling                             | 90  |

|    |       | 7.2.4 | 4 (        | Our Motivation                                                                  | 91  |

|    | 7.3   | Desig | ign        | and Challenges                                                                  | 92  |

|    |       | 7.3.1 | 1 ′        | Two-level Parallelism                                                           | 92  |

|    |       | 7.3.2 | 2          | Stream Processing Scheme                                                        | 95  |

|    |       | 7.3.3 | 3 ′        | Two-level Lock System                                                           | 98  |

|    |       | 7.3.4 | 4          | Data Access Pattern                                                             | 01  |

|    | 7.4   | Impl  | lem        | nentation                                                                       | 02  |

|    |       | 7.4.1 | 1          | Dependency Array Structure and Transfer                                         | .03 |

|    |       | 7.4.2 | 2          | Stream Indexing                                                                 | .04 |

|    |       | 743   | 3 1        | Code for Lock Functions                                                         | 06  |

|         | 7.4.4 | Flow of Tile Processing           |

|---------|-------|-----------------------------------|

| 7.5     | Expe  | rimental Evaluation               |

|         | 7.5.1 | Experimental Background and Setup |

|         | 7.5.2 | Experimental Results and Analysis |

| 7.6     | Sum   | mary                              |

| Chapter | 8     | Conclusion                        |

| Chapter | 9     | List of Publications              |

| Referen | ces   |                                   |

| Abstrac | t     |                                   |

| Autobio | orant | ical Statement                    |

# LIST OF TABLES

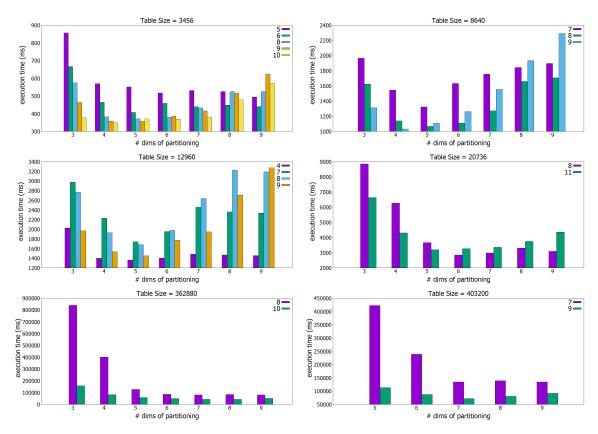

| Table 1  | DP-table Size = $3456$                                                           |

|----------|----------------------------------------------------------------------------------|

| Table 2  | DP-table Size = 8640                                                             |

| Table 3  | DP-table Size = 12960                                                            |

| Table 4  | DP-table Size = 20736                                                            |

| Table 5  | DP-table Size = 362880                                                           |

| Table 6  | DP-table Size = 403200                                                           |

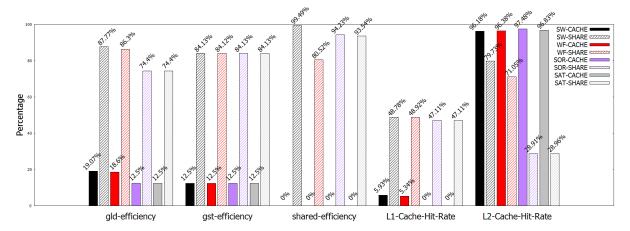

| Table 7  | Profiling data for cache-based and shared memory-based mechanisms on GTX 1080 Ti |

| Table 8  | Execution time (ms): averaged for 100 repetitions 79                             |

| Table 9  | Performance data for the GTX 1080 Ti GPU                                         |

| Table 10 | Performance data for the Tesla K40 GPU                                           |

| Table 11 | Number of time steps can be processed for each pair of tile size and distance    |

| Table 12 | Performance in GFLOPS for Moore Neighborhood Pattern                             |

| Table 13 | Performance in GFLOPS for Cross-Shaped Neighborhood Pattern 112                  |

| Table 14 | Performance Comparison in GFLOPS for Cross-Shaped Neighborhood Pattern           |

| Table 15 | Performance Comparison in GFLOPs per second for Moore Neighborhood Pattern       |

# LIST OF FIGURES

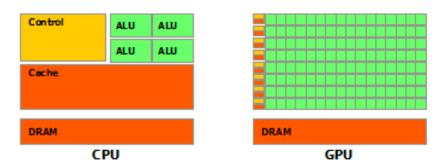

| Figure 1  | The GPU denotes more processing cores and small cache and less sophisticated flow control                             | 9   |

|-----------|-----------------------------------------------------------------------------------------------------------------------|-----|

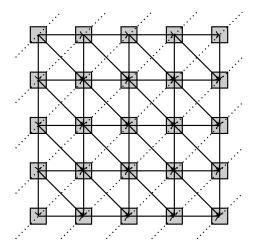

| Figure 2  | The wavefront parallelism                                                                                             | 16  |

| Figure 3  | Hyperplane Tiling vs Square Tiling.                                                                                   | 17  |

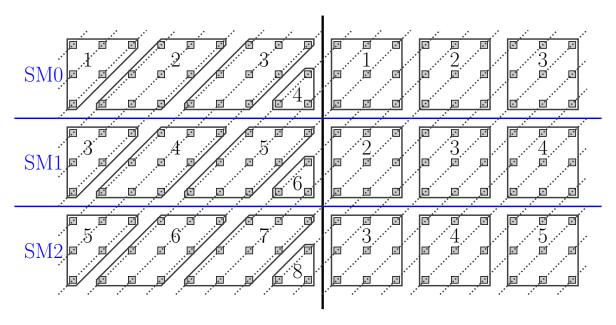

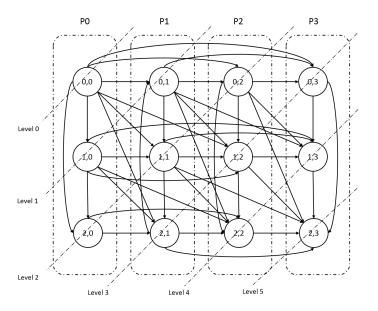

| Figure 4  | Partitioning a 3-D <i>DP-table</i> by a divisor $(3,3,3)$                                                             | 32  |

| Figure 5  | Dependency graph for $OPT(2,3)$                                                                                       | 34  |

| Figure 6  | The number of non-zero dimensions influence the performance                                                           | 50  |

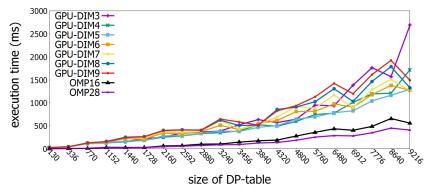

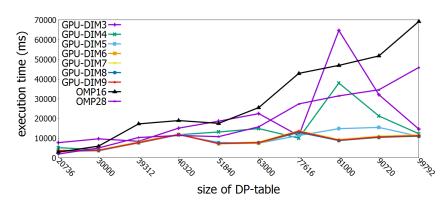

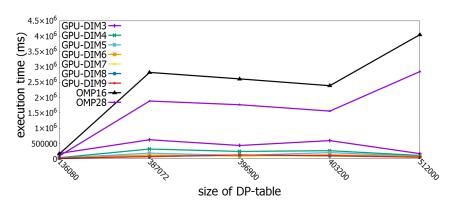

| Figure 7  | Average running time vs. the size of <i>DP-table</i>                                                                  | 53  |

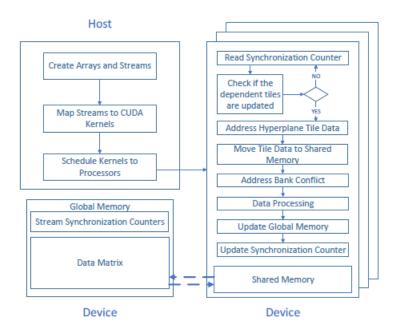

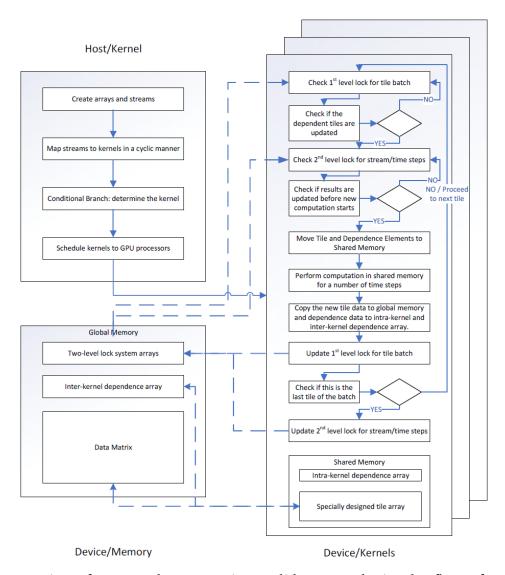

| Figure 8  | Design of Host and GPU Device: solid arrows depict the flow of events and dashed arrows show the data communication   | 61  |

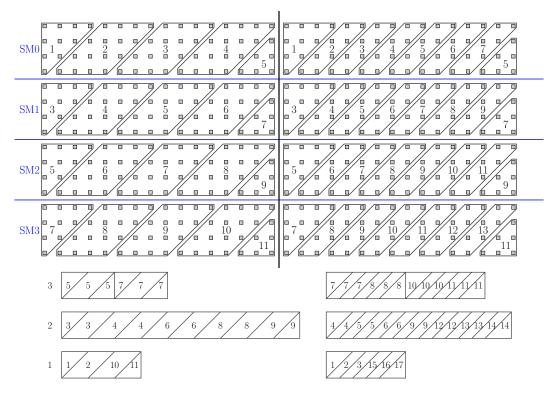

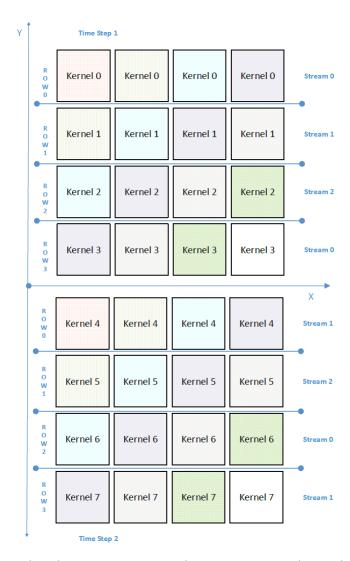

| Figure 9  | The comparison of inter-tile concurrency for two different tile sizes                                                 | 64  |

| Figure 10 | Data layout in global memory and shared memory                                                                        | 69  |

| Figure 11 | Shared memory-based mechanism achieves much higher efficiency rate on multiple metrics except L2 cache hit rate       | 77  |

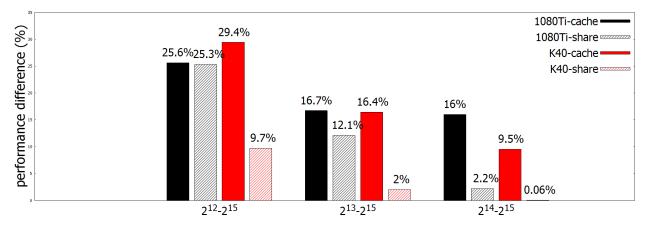

| Figure 12 | Average difference for four applications                                                                              | 83  |

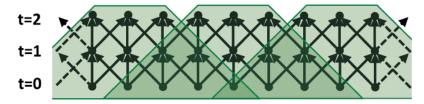

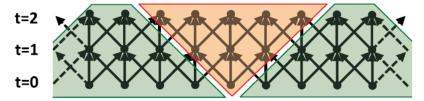

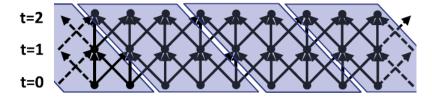

| Figure 13 | Different tiling strategies [1] illustrate the tradeoff between concurrency, computation overhead, and memory latency | 86  |

| Figure 14 | Design of Host and GPU Device: solid arrows depict the flow of events and dashed arrows show the data communication   | 93  |

| Figure 15 | Intra-tile parallelism and inter-tile parallelism                                                                     | 94  |

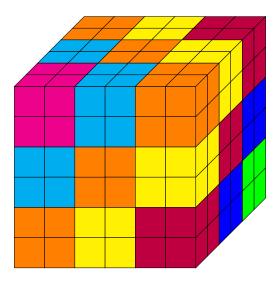

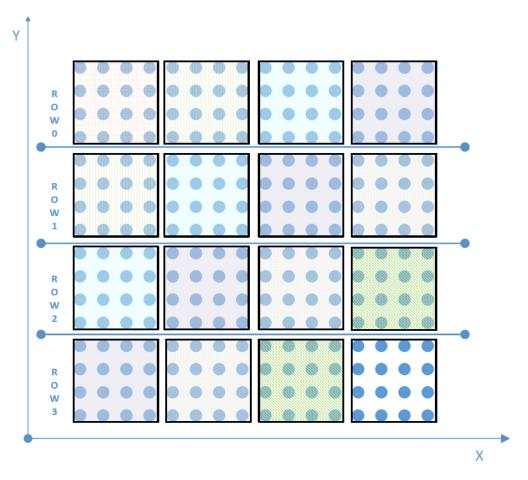

| Figure 16 | Tiles that are in same color are processed simultaneously                                                             | 95  |

| Figure 17 | Shared memory organization for dependent elements and tile elements.                                                  | 101 |

| Figure 18 | Two patterns lead to different memory efficiency                                                                      | 109 |

### **CHAPTER 1 INTRODUCTION**

A nested loop is a loop that contains another loop or another nested loop. Generally, executing a nested loop requires memory access to one or multiple data entries, which are addressed by the indexes of one or multiple loops. Thus, the memory layout of a nested loop can be depicted in a multi-dimensional block where the dimensions of the block match the depth of the nested loop. In many problems, a nested loop can lead to a tremendous number of operations even if the length of each loop is not unacceptable long. A typical solution for accelerating this process is to split the total workload into small pieces and executing these pieces concurrently. In parallel programming, a nested loop can be split into multiple blocks along either one or more loops. Thus, each block contains a smaller nested loop, which is processed by one OS thread.

The idea of accelerating nested loops on GPUs is similar, but a much greater concurrency can be achieved because of the massive threads capacity. In GPU programming, it is recommended to split a nested loop completely into iterations, instead of a small block of a nested loops and each thread processes one iteration only. The ability of achieving huge concurrency also makes GPUs efficient in solving nested loop problems.

Nested loops are used in a variety of problems and this dissertation discusses the work for optimizing nested loops, in Dynamic Programming (**DP**) problems [2, 3] and stencil problems [4, 5] on GPUs. In dynamic programming problems, each data entry is updated in place, so data dependence exists between the data entries, which prevents the loop from being fully parallelized and leads to loop-level parallelism, often called DOACROSS parallelism [6]. Thus, maximizing concurrency according to the synchronization primitives,

in the statement, is important to optimizing dynamic programming problems. In stencil problems, data entries are updated out of place at each time stamp, so there is no data dependence to restrict the concurrency and the statements within a loop can be executed independently. Thus, nested loops in stencil problems can be fully parallelized as DOALL parallelism [7]. In both cases, poor data locality and irregular workload can hurt the performance even though the code has obtained concurrency that can fully utilize compute capability.

Parallel implementation of some dynamic programming problems follows a specific data access pattern, which leads to *wavefront parallelism* [8]. All previously mentioned performance issues exist in the wavefront parallelism execution process. In most cases, obtaining large concurrency and balanced workload can notably increase the performance. This strategy is applied [9] and achieves a significant speedup on GPUs, which is 25 times faster than the multicore parallel implementation. The details of the work is presented in chapter 5.

Moreover, having good data locality can further improve the performance when the data entries, required by the computation, cannot completely fit into the L1 cache. GPU offers a user-managed cache, called shared memory, to help with this optimization. Under certain circumstances, manually organizing the data entries in shared memory can significantly increase data reuse and reduce the number of memory transactions. In chapter 6, a data locality optimization work is presented, which obtains a sixfold speedup.

Similarly, no-dependence nested loops can be optimized if the data locality is improved without introducing extra high latency. In stencil problems, good data locality is obtained by reusing the cached data entries to calculate as many time stamps as possible. A popular

method, which is called overlapped tiling and studied in many existing works, like [10, 11, 12, 13], obtains both significant concurrency and good data locality. However, it also leads to issues like an imbalanced workload and repeated calculations.

In this dissertation, the tiling methods for optimizing the loop-level parallelism for nested loops on GPUs are presented and discussed. DOACROSS and DOALL parallelism are explored in Dynamic Programming problems and stencil problems, respectively. The proposed tiling approaches resolve data locality and workload balancing issues when dealing with DOALL parallelism and also consider the concurrency for DOACROSS parallelism.

### 1.1 Contributions

In this dissertation, we develop non-overlapped tiling optimization strategies for both DOALL and DOACROSS parallelisms for nested loops on GPUs. We propose three approaches and make the following contributions to the nested loop optimization on GPUs.

• The first contribution is the development of a parallel approximation algorithm for  $P \mid\mid C_{max}$  based on the Polynomial Time Approximation Scheme PTAS, which is specially designed for GPUs. The parallel algorithm [14] requires solving a higher-dimensional dynamic programming problem and is based on parallelizing the PTAS [15]. The major challenge of making approximation algorithms, such as the one for  $P \mid\mid C_{max}$ , efficient on GPUs is to improve the execution time of the higher-dimensional dynamic programming procedure. We take into account the huge computing power offered by modern GPUs and exploit the potential DOACROSS parallelism. The proposed solution resolves the memory issues and improves the thread-level workload balance. To the best of our knowledge this is the first GPU approximation algorithm

for solving the problem on shared-memory systems, proposed in the literature. Our evaluation on the GPU considers as many as nine dimensions in order to assess the optimal decomposition of the various problem instances. We compare the performance of our GPU implementation with that obtained by the OpenMP implementation on a multicore CPU. The results show that our techniques yield an efficient GPU approximation algorithm for  $P \mid\mid C_{max}$ , with improved performance on large problem instances.

- In the second research component, we exploit the wavefront parallelism for 2D dynamic programming problems and 2D stencil problems, which are updated in place. We design a shared memory-based tiling mechanism to achieve balanced and optimized workloads with minimal overhead compared to existing state-of-the-art approaches. In addition, we provide a methodology for deriving the optimized thread blocks and tiles from the GPU architecture. We design the kernel configuration to significantly reduce the minimum number of synchronizations required and also introduce an inter-block lock to minimize the overhead of each synchronization. Moreover, GPU shared memory is used to replace the L1 cache for improving both spatial and temporal locality, showing that a shared memory-based approach achieves better data locality and coalesced global memory access than a cache memory approach [8] does. To the best of our knowledge, there is no existing work that addresses both the concurrency issue and the memory efficiency issue.

- Our third contribution is the development of a non-overlapped tiling approach for optimizing 2D stencil problems by tiling the time dimension. Unlike the overlapped

tiling approach, non-overlapped tiling does not have the required data entries to perform repeat calculations to reproduce the data lost along the temporal dimension, which makes non-overlapped tiling not feasible for optimizing the time dimension. In our development, we make time dimension tiling possible in the non-overlapped tiling optimization by using GPU shared memory and developing a data pattern for accessing the tiles in shared memory. In addition, we explore the tile-level parallelism in a stream-processing pattern and design a two-level lock system to coordinate the processing sequence. The streaming system tiles the time dimension and does not generate extra calculation and imbalanced workload. Moreover, the proposed non-overlapped tiling approach is developed as a general purpose implementation for solving the most frequently used 2D stencil computations, which have different number of stencil points.

The optimization methods presented in this dissertation use CUDA terminology and use NVIDIA GPUs as experimental hardware. Because the research is using shared memory for improving memory efficiency, our contributions can be obtained when the users can access and manipulate GPU shared memory directly.

#### 1.2 Dissertation Outline

The dissertation is organized as follows. Chapter 2 gives a brief overview of NVIDIA GPUs and the related CUDA API. Chapter 3 describes the tiling strategy to optimize DOALL and DOACROSS parallelisms by comparing square tiling to non-square tiling and overlapped tiling to non-overlapped tiling. Related works of my three dissertation projects are presented in chapter 4. Chapter 5 describes the tiling style data-partitioning method

that adjusts the over-sized data matrix into GPU memory and fully utilizes the compute resources for DOACROSS parallelism on high-dimensional dynamic programming. Chapter 6 describes a highly optimized hyperplane tiling approach, which achieves a balanced workload and maximum resource utilization with an extremely low synchronization overhead, for improving wavefront parallelism on GPUs. Chapter 7 extends some of the ideas from Chapter 4 to develop a non-overlapped tiling approach that optimizes the 2D stencil problems by tiling the time dimension on GPUs. The non-overlapped tiling approach can be adapted for different stencil types. At the end, we make a conclusion for our dissertation work and discuss some of the future research directions in Chapter 7.

### CHAPTER 2 OVERVIEW OF NVIDIA GPUS AND CUDA

GPU computing is a popular approach to simulating complex models and performing massive calculations. Compared to the typical multicore CPUs, the developers can obtain much higher throughput from the latest Nvidia GPUs without consuming extra energy. The high throughput implies a greater potential for accelerating the intensive arithmetic calculations on the GPUs. Thus, the extensive research on developing optimal GPU applicable parallel algorithm is required in many fields. Efficient GPGPU, known as General-Purpose computing on Graphics Processing Units, requires good parallelism, memory coalescing, regular memory access, small overhead on data exchange between the CPU and the GPU, and few explicit global synchronizations, which are usually gained from optimizing the algorithms. Besides these advantages, the proper use of some novel properties provided on NVIDIA GPUs can offer further improvement.

On GPU devices, software developers are able to develop general purpose processing applications using the CUDA platform. CUDA (Compute Unified Device Architecture) is a parallel computing platform and application programming interface (API) model created by NVIDIA [16]. The CUDA platform provides direct access to the GPU's virtual instruction set and parallel computational elements, for the execution of compute kernels.

In this chapter, we briefly introduce two different NVIDIA GPU architectures that we use for performance evaluations as well as the major GPU features and relevant CUDA concepts.

### 2.1 GPU Architecture

A NVIDIA GPU is designed with multiple streaming multiprocessors and a global memory system that includes a high bandwidth unified memory [17, 18, 19] and an L2 cache shared by all the multiprocessors. In each multiprocessor, there are hundreds of processing cores, which must execute the same operation concurrently like a vector processing unit. In addition, a multiprocessor is also equipped with an L1 cache and a human-managed cache, called shared memory. In this dissertation, we evaluate the experimental performance and architecture of Kepler [17] and Pascal [18] GPU architectures.

Streaming Multiprocessors (SMs) are the part of the GPU that runs CUDA kernels. Each multiprocessor has its own processing cores, cache blocks, registers, and control units. A Kepler GK110 GPU includes 15 streaming multiprocessors and each multiprocessor is equipped with 192 cores and a 64 KB cache block, which can be partitioned between L1 cache and shared memory. A Pascal GP104 GPU includes around 20 streaming multiprocessors and each multiprocessor is equipped with 128 cores. Unlike the Kepler GK110 architecture, a Pascal GPU has a 96 KB shared memory block, which is separate from the individual 48 KB L1 cache, in each multiprocessor.

The 1080 Ti has a total of 3584 CUDA cores, 12 GB global memory, and each CUDA core has a clock rate of 1.63 GHz for a peak performance of around 11.6 TFLOPS. Whereas, the K40 is equipped with 12 GB memory and has 2880 cores at a clock rate of 745 MHz, which sum to a peak performance of 4.29 TFLOPS. In addition, the memory bandwidth of the GTX 1080 Ti and Tesla K40 are 484 GB/s and 288 GB/s, respectively. We divide the throughput by the memory bandwidth to calculate the arithmetic intensity as 24 FLOPs/byte for 1080 Ti

Figure 1: The GPU denotes more processing cores and small cache and less sophisticated flow control.

and 15 FLOPs/byte for K40.

**GPU Cores** The GPU is designed into a highly parallel architecture that has tremendous computational horsepower and very high memory bandwidth [16]. As it is shown in Fig. 1, unlike the traditional multicore CPUs, the GPUs are equipped with more than a thousand cores where each core has a lower clock rate and a much smaller and simpler cache. Therefore, GPUs are designed for intensive data processing rather than data caching and flow control.

Shared Memory can be used as a managed cache, which is especially useful when operations are performed on a certain block of data entries that are not stored consecutively. Significant benefit is obtained when using shared memory instead of cache in the study of matrix multiplication [20, 21]. Especially when the cache behavior is unpredictable, storing these data entries in shared memory guarantees data reuse. Also, it is more beneficial to use shared memory on Pascal GPUs because using shared memory frees L1 cache from storing non-contiguous data, which may lead to more efficient L1 cache usage.

### 2.2 CUDA Terminology

CUDA provides programmers with APIs for accessing a GPU's virtual instruction set and computing resources.

**Kernel:** A CUDA kernel consists of the operations, which are executed N times in parallel by N different CUDA threads on one or multiple multiprocessors.

**Thread:** In CUDA programming, threads are the basic processing unit that process the kernel's operations. CUDA threads do not have individual task schedulers, so a group of threads that share the same scheduler perform the same operations. To manage that many threads launched in a kernel, each thread is indexed with a unique ID.

Thread Block: In CUDA programming, a kernel function is launched with one or multiple thread blocks where a thread block is a programming abstraction which manages the thread and memory resources. First, a thread block is a cluster of threads, which contains up to 2048 or 1024 threads for different architectures. Second, the thread block manages memory access. Threads within the same block can access the same shared memory and L1 cache; however, data access between multiple blocks can only be completed in global memory. Third, a thread block resides only on one multiprocessor and the threads within a block share the in-processor memory and registers.

Warp: The multiprocessor creates, manages, schedules, and executes threads in groups of 32 parallel threads called warps [16]. Thread blocks are partitioned into warps and each warp contains threads of consecutive, increasing thread IDs. A warp is like a SIMD (Single Instruction Multiple Data) machine, which can only execute one instruction with multiple data at one time. On Kepler and Pascal GPUs, full efficiency is realized when all 32 threads

of a warp agree on their execution path. If threads of a warp diverge via a data-dependent conditional branch, the warp executes each branch path taken, disabling threads that are not on that path. Branch divergence occurs only within a warp; different warps execute independently regardless of whether they are executing common or disjoint code paths.

Stream: A stream is a sequence of operations that execute in issue-order on the GPU. Thus, kernels scheduled to the same stream are executed in serial. To perform multiple CUDA kernels simultaneously, each kernel has to be launched in a unique stream. In some circumstances, launching kernels in multiple streams helps with obtaining maximum

### 2.3 **GPU Properties**

The GPU is designed for massive parallelism, which requires many cores to fulfill the concurrency requirement. Thus, the delicate cache design is sacrificed on GPUs to tradeoff the performance and power cost. In order to fully utilize the GPU computing power, the programmers have to pay attention to a couple of GPU properties.

performance by leveraging concurrency and hiding data communication costs.

Memory Hierarchy: GPUs have a multi-layered memory hierarchy designed for different execution scope. In each thread block, registers are evenly assigned to each thread as its private memory. Then, each thread block has shared memory, which is on-chip and visible to all threads of the block. Shared memory can be used as managed cache with much higher bandwidth and much lower latency than global memory. Thus, data communication between the threads of a block can be performed in shared memory. In addition, each processor is also equipped with an on-chip L1 cache, used for fetching and storing data from off-chip memory. Also, a L2 cache is off-chip and accessible by all the processors.

The largest memory unit on a GPU is global memory, which is off-chip and all threads have access to. On a GPU, memory transactions are initiated by warps, where each warp consists of 32 threads and a warp can process only one instruction at a time. Global memory is accessed via 32, 64, or 128-byte memory transactions with the first address of each write or read memory transaction memory aligned to a multiple of the transaction size. When a warp performs a global memory access, it coalesces the memory accesses of the threads within the warp into one or more of these memory transactions depending on the size of the word accessed by each thread and the distribution of the memory addresses across the threads. Therefore, highest throughput can be achieved if 32 threads in a warp request contiguous data entries that are aligned (memory coalescing). If 32 threads read data entries located at non-contiguous addresses, it is possible that this warp performs up to 32 memory transactions to complete the memory request.

Bank Conflict: Shared memory is organized into banks, which are equally-sized memory modules and should be accessed simultaneously to obtain high bandwidth. However, if multiple addresses of a memory request fall in the same memory bank, there is a bank conflict and the access must be serialized. On the other hand, n addresses of a memory read or write request that fall in n distinct memory banks can be satisfied simultaneously [16]. Stream Processing: On GPUs, each stream has its own operating context so that it may execute its commands out of order with respect to the other streams. Each stream can include multiple thread blocks and may utilize one or more GPU processors. The processor assignment of these thread blocks is not guaranteed and different streams could be distributed to the same processor during execution. Stream processing on GPUs is the technique to process multiple kernel functions concurrently, where each kernel launched

in a different stream. Thus, multiple kernel functions can be processed concurrently when each kernel is associated with an individual stream. However, multiple kernel functions that are assigned to the same stream are processed in sequence. Therefore, the number of concurrently processed kernel functions is limited by the number of streams as long as it is within the GPU capability. When we assign only one thread block to each kernel function, a mapping between the blocks and the streams is created. If the number of streams is the same as the number of processors, we will have one thread block processed in each processor because a GPU distributes the thread blocks evenly to all available processors.

### CHAPTER 3 OVERVIEW OF LOOP TILING

The loop tiling technique is used to improve data locality in a large-scale computation to ensure that the data entries in a tile fit perfectly into cache memory so that data can be reused. In addition, loop tiling also helps with obtaining better workload balance when data dependence exists within the nested loop.

### 3.1 Loop Tiling on GPUs

Tiling loops on a GPU can be completed in two steps. First, the loops are partitioned into small chunks in the host code. Thus, the parallelism is split into two level parallelism: inter-tile parallelism and intra-tile parallelism. Second, launching the tiles in one or multiple kernels is used to obtain the inter-tiles parallelism, and intra-tile parallelism is achieved by processing the inner iterations of each tile on the threads.

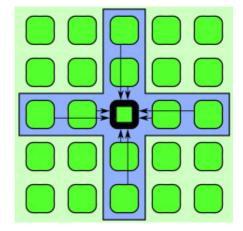

There are two approaches for obtaining inter-tile parallelism. One is that all the tiles are launched within the same kernel and processed by different thread blocks, so it generates a tile-block mapping. Streaming processing provides the alternative, which launches multiple kernels simultaneously. In this approach, one or multiple tiles are assigned to the thread blocks of a kernel, and multiple kernels are assigned to the streams. Therefore, the tiles that reside in the different stream context can be processed simultaneously.

Because the multiprocessor is equipped with many cores and limited memory capability, the tiling performance on GPUs is determined by the size of each tile. A large tile brings in enough concurrency but its memory requirement may exceed the GPU's memory capacity. On the other hand, a small tile can fit into the in-processor memory block but the concurrent workload may be insufficient for maximizing the use of the compute power.

### 3.2 Wavefront Parallelism

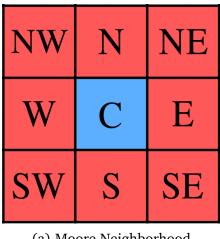

In a two-dimensional data matrix, wavefront parallelism can be visualized as the computation proceeding along diagonal waves, because each data entry is updated based on the already updated neighboring entries occurring in the same row, column, and diagonal if the dependence is uniform. A problem has uniform dependences if each data entry depends on a constant number of dependent subproblems as well as having a constant distance between itself and any one of its dependent subproblems, such as the local sequence alignment problem [2, 22]. Problems like matrix parenthesization [22] and the  $P \parallel C_{max}$  [9] have non-uniform dependence. Fig. 2 illustrates the wavefront parallelism on a data matrix where each data entry has uniform dependence on its top and left cells. Data entries that reside in the same anti-diagonal, illustrated as dotted lines, could be executed concurrently since they depend on two adjacent entries at one preceding antidiagonal level, where the dependencies are depicted as arrows. To obtain good concurrency, wavefront parallelism is often applied to applications that have nested loops and uniform dependences across iterations [23, 24, 25, 26]. Wavefront parallelism exploits the potential parallelism but it does not guarantee the efficiency of the parallel computation. The bi/tri-directional dependencies restrict the parallelism in the diagonal order, which can result in an imbalanced workload and poor data locality. To solve large problems, efficient approaches are required to eliminate these performance issues.

### **Tiling Technique**

The tiling technique is used to improve data locality in a large-scale computation to ensure that the data entries in a tile fit perfectly into cache memory so that data can be

Figure 2: The wavefront parallelism.

reused. Fig. 3 shows two data matrices for the same DOACROSS parallelism, separated by the middle vertical line. The small squares in this picture represent the data entries and each data entry depends on the neighbors to its left and top. Thus, each data entry has a dependence in both outer loop and inner loop, which results in the fact that concurrency can be achieved along the diagonal direction. The dotted lines represent the concurrency that the data entries on the same dotted line can be executed simultaneously. In Fig. 3, the square tiling method generates two-level parallelism, which is shown on the righthand side of the vertical line. Inter-tile parallelism, represented by the tile indices, executes the concurrent tiles on multiple streaming multiprocessors and intra-tile parallelism, represented by the dotted lines, proceeds along diagonals, allowing concurrent data entries to be calculated by CUDA cores.

Figure 3: Hyperplane Tiling vs Square Tiling.

### 3.2.1 Square VS Non-Square

Naturally, loop tiling partitions the loops evenly into multiple square-shaped tiles, as shown on the righthand side of Fig. 3. Square tiling improves the performance of DOALL parallelism because it contributes to efficient cache utilization. However, square tiling may not contribute optimal performance to DOACROSS parallelisms because an imbalanced workload still exists in both inter-tile parallelism and intra-tile parallelism and the average concurrency is relatively low.

Hyperplane tiling splits the data entries along the diagonals, which changes the data layout accessed by the memory operations and eliminates the intra-tile imbalanced workload. As shown in Fig. 3, hyperplane tiling, on the lefthand side of the vertical line, obtains balanced intra-tile workload in the parallelogram tiles. An imbalanced intra-tile workload appears only at the first and last tiles of each row; this overhead is negligible when the matrix size is large. The hyperplane tiling technique achieves a balanced intra-tile workload;

however, it is not necessarily efficient due to the imbalanced inter-tile workload caused by synchronization latency – the hyperplane tiles have to be synchronized with a global barrier to ensure the correctness of inter-tile data communication. Also, the global barrier forces all concurrent tiles to wait for the completion of the longest running task and idles some streaming multiprocessors. In this case, hyperplane tiling is a better option, which changes the data layout accessed by the memory operations and eliminates the intra-tile imbalanced workload.

### CHAPTER 4 RELATED WORK

### 4.1 Higher-Dimensional Dynamic Programming

To address "the curse of dimensionality", some researchers proposed approximations for higher-dimensional dynamic programming [27, 28, 29]. Despite huge advances in parallel computing, the parallel implementation of exact higher-dimensional dynamic programming problems, especially on the GPU, is not as well-studied as two-dimensional dynamic programming. Berger and Galea [30] implemented a multi-dimensional knapsack algorithm on the GPU by introducing the idea of combining coarse-grained parallelism and fine-grained parallelism, and improving the memory coalescing by fixing the number of dimensions. However, their technique works only for small problem sizes, as the size of a higher-dimensional table can grow quickly with the number of dimensions and is likely to exceed the GPU global memory.

Previous work investigated parallel dynamic programming, considering both coarse-grained (multiprocessor clusters) and fine-grained architectures (multicore CPUs, and many-core GPUs). A coarse-grained architecture, such as a multiprocessor cluster, usually achieves efficient local computations because of its powerful computational capabilities and large memory on each processor. But the inefficient inter-cluster communication and unbalanced workload are detrimental to the parallel performance. Some prior research has focused on reducing the inter-cluster communication, such as, partitioning the dynamic programming table into multiple rectangular segments [31, 32, 33]. In addition, work distribution schemes, like block-cyclic [32], have also been employed to balance the workload across processors. Implementing parallel dynamic programming on multi-

core CPUs and many-core GPUs requires a more sophisticated method of work distribution among threads, as a fine-grained architecture has many more computing resources to run the same anti-diagonal levels of sub-problems concurrently, especially for the GPU. A strategy for computing successive anti-diagonals of the dynamic programming table was applied to the multicore CPU to maximize parallel execution [14, 34]. Several researchers [35, 36, 37, 38] extended this strategy to achieve more fine-grained parallelism on the GPU, mostly for two-dimensional dynamic programming problems. Very few researchers investigated accelerating higher-dimensional dynamic programming problems on the GPU.

To address "the curse of dimensionality", some researchers proposed approximations for higher-dimensional dynamic programming [27, 28, 29]. Despite substantial advances in parallel computing, the parallel implementation of exact higher-dimensional dynamic programming problems, especially on the GPU, is not as well-studied as two-dimensional dynamic programming. Berger and Galea [30] implemented a higher-dimensional knapsack algorithm on the GPU by introducing the idea of combining coarse-grained parallelism and fine-grained parallelism, and improving the memory coalescing by fixing the number of dimensions.

## 4.2 Wavefront Parallelism Optimization

#### **Cache-Oblivious Wavefront**

A cache-oblivious technique has been applied to wavefront parallelism recently [39]. As for other matrix-based applications, the data matrix is recursively split into smaller chunks until it can fit into cache so that data locality is improved. However, implementing

this cache-oblivious approach on GPUs is challenging because of the SIMT architecture. The recursive functions would consume limited GPU on-chip memory and it is difficult to distribute recursions to massive threads.

### **Compensation-based Parallelism**

The compensation-based method is another approach introduced in [40, 41, 42], which breaks the multi-directional dependencies by ignoring the row-order data dependency. The data entries in the same row are executed concurrently and a correction is then applied to the intermediate results. Without the row-order data dependency, the execution is completed with a balanced workload. However, this method is not generic, because it changes the original data dependency as well as the sequence of computation operators on data entries [42]. Moreover, domain knowledge is required for correcting the final results, which makes this method difficult for users who have no related background.

### **Tiling Technique**

On the other hand, the tiling technique is a general solution that can be applied to all problems of this kind. The idea of using the wavefront technique and tiling technique to maximize the innermost loop parallelism was first presented by Wolf and Lam [43]. The wavefront technique transforms the nested loop and makes the innermost loop a *DOALL*, so that maximized parallelism is obtained in the innermost loop. Then, the tiling technique reduces the synchronization cost and improves data locality. The square tiles used in the proposed algorithm cause an imbalanced workload issue on GPUs because the in-tile workload cannot be evenly distributed to the many threads. Also, this algorithm cannot be applied to the GPU directly because it does not map each data entry to the threads.

Di et al. [44, 26] adapt this tiling algorithm to GPUs to accelerate the successive over-

relaxation (SOR)-based applications. In these works, the square tiles are distributed to thread blocks so that each tile is processed by a GPU streaming multiprocessor and each thread processes one or more data entries within the tiles. However, only the tiles on the same diagonal can be processed concurrently because the outermost parallelism is achieved along the anti-diagonal. This leads to a processor-level concurrency issue at the beginning and the end of the execution, since the number of concurrent tiles is fewer than the number of processors. Moreover, due to the limited cache size on GPUs, the use of square tiles cannot improve the data locality in the L1 cache.

Malas et al. [45] accelerate stencil operations with hyperplane tiles on multicore CPUs and achieves about 2 to 3 times speedup comparing to the square tiling implementations. Bednárek et al. [3] apply the hyperplane tiling technique to their GPU implementation, which solves edit distance problem efficiently. The enhanced implementation not only minimizes the imbalanced workload but also optimizes the thread concurrency. Bednárek ignores the memory issue because the intermediate data entries are not needed in this work; therefore, most of the calculations can be performed using L1 cache. Di et al. [46] present a compiler framework that automatically parallelize nested loops on GPUs. In this work, the data matrix is split into hyperplane tiles and data entries of each tile are moved to shared memory before the execution, which enables coalesced memory access. However, this framework can only parallelize nested loops that have no dependence.

A GPU stream processing approach that reduces the synchronization cost and improves the processor-level concurrency is proposed by Belviranli [8]. In this implementation, a row of tiles are processed at the same processor, so local synchronization between each pair of these tiles is sufficient. Thus, the original global barriers can be eliminated and unnecessary idle waiting is greatly reduced at each processor. But memory efficiency is not optimized. Because concurrent data entries are neither aligned nor consecutively stored in global memory, uncoalesced global memory accesses are inevitable and result in relatively inefficient memory access. Also, due to the limited cache size, it is difficult to reuse the cached data because each warp has to release its cache lines when accessing new data entries.

#### **Shared Memory**

On GPUs, shared memory can be used as a managed cache, which is especially useful when operations are performed on a certain block of data entries that are not stored consecutively. Significant benefit is obtained when using shared memory instead of cache in the study of matrix multiplication [20, 21]. The tiling technique is applied in matrix multiplication to reduce the number of data entries to be calculated concurrently, so these data entries can fit into shared memory. Due to the unpredictable cache behavior, storing these data entries in shared memory guarantees data reuse. Also, on the GPUs that have separate L1 cache and shared memory, using shared memory frees L1 cache from storing other non-contiguous data, which may lead to more efficient L1 cache usage.

## 4.3 Time-Space Tiling for Stencil Computation

The optimization of stencil computations has been studied for decades and they are still challenging for state-of-the-art multi-core and many-core architectures because of high memory bandwidth requirements. Since the array size is usually much larger than cache capacity, the computation forces subsequent sweeps through the array to reload data, which results in poor temporal locality.

The major solution is time-space tiling, which minimizes the space dimension's cache misses and reuses the cached data along time dimension. This strategy is widely used in most recent work [10, 47, 1, 12, 11, 48, 49, 50, 51, 52]. Various implementations are proposed to achieve the same objective but lead to different effectiveness according to the device architectures and the tradeoff between computation overhead and memory latency.

### **Overlapped Tiling**

Overlapped tiling optimization performs redundant operations to address the dependence data when executing more than one time step. Krishnamoorthy [11] characterizes the situations in which tiling inhibits concurrent start and defines overlapped tiling approaches that enable concurrent start in the tiled space and resolve the load imbalance caused by tiling. Rawat et al. present a method for obtaining the optimal tile size and improve the overlapped tiling efficiency by managing GPU memory resources [12, 13]. Then, Rawat further improves the overlapped tiling with a fusion heuristic, which consumes more register resources to enable better temporal locality and reduce memory traffic [1]. Yount [49] specifically designed an overlapped tiling approach for the Intel Xeon Phi processor that utilizes the Phi processor's high-bandwidth memory, and optimizes the computation with SIMD instructions and vector-folding. Meng [52] points out the relationship between the performance and ghost zone of overlapped tiles and provides a method for finding the optimal ghost zone size automatically. Nguyen et al. [10] present a 3.5Dblocking algorithm to address 3D stencil problems with overlapped tiling. The 3.5D tiling performs 2.5D-spatial tiling and temporal tiling, which makes the 3D stencil computation no longer memory bandwidth bounded. A flexible load-balancing scheme is also provided for distributing the array elements equally to the threads on both CPUs and GPUs. In addition, some code auto-generating compilers [53] have been built on top of overlapped tiling, like Halide [54], PATUS [55].

### **Split Tiling**

Split tiling enables concurrent start without introducing computation overhead. However, it has trouble with intra-tile parallelism due to the tile shape. Krishnamoorthy [11] develop a split tiling approach by dividing a tile into sub-regions and scheduling the computation and communication to achieve concurrent start and load-balanced execution. Bondhugula [56] proposes a formalized diamond tiling, which is generalized to arbitrary stencil computations. This approach formalizes the conditions for the concurrent start for tiling hyperplanes and provides an approach to find such tiling hyperplane. Grosser et al. [48] split the tiles into a sequence of trapezoidal computation steps and develop an approach for generating split tiling code for GPUs in the PPCG [57] code generator. The proposed algorithm performs split tiling for stencil computations that have an arbitrary number of dimensions without the need for skewing or redundant computations. Malas et al. [45] combine the ideas of multicore wavefront temporal tiling with diamond spatial tiling to reduce memory bandwidth intensity in a 3D space grid, which shows performance advantages in bandwidth-starved computations and is optimized for multicore CPUs. Shrestha et al. [58] develop a jagged polygon tiling technique, which is a variant of diamond tiling. The jagged polygon tiling obtains the advantages of concurrent start and exploits inter-tile locality without compromising intra-tile parallelism.

#### **Cache Oblivious**

Cache Oblivious [59, 5] solutions are an alternative for resolving frequent memory access issues, which shares the same property of blocking time-space dimensions. In a

cache oblivious implementation, the blocking size is automatically determined to fit into the cache memory, which is achieved by continuously tiling the longer dimension in the recursive kernels. Bilardi [60] develops a cache oblivious algorithm for the problem of simulating large parallel machines on smaller machines in a time-space optimization manner. The algorithm applies to 1D and 2D spaces but does not generalizes to higher dimensions. Frigo [61] presents a more generalized cache oblivious algorithm for stencil computations, which solves arbitrary stencils computations in n-dimensional spaces. Tang et al. [62] develop a compiler and runtime system, called Pochoir, for implementing stencil computations on multicore CPUs. The Pochoir compiler is employed with a parallel cache-oblivious algorithm and it translates a domain-specific stencil language embedded in C++ into high-performing Cilk code for general n-dimensional stencil computations.

### **Time Skewed Tiling**

Time skewed tiling tiles the temporal dimension according to the inter-tile dependence, which usually results in rectangular shapes in 1D computations, parallelogram tiles in 2D, and parallel-piped in 3D. Wonnacott [63] proposed the idea of a time skewing transformation to produce scalable locality for optimizing the computations, where data locality is the dominant issue. Later, this tiling optimization is used to eliminate the redundant computations [64, 65]. Andonov et al. [66, 67] discuss the method for selecting the optimal tile size for time skewing in a 2D grid.

#### **Hybrid Tiling**

Some attempts for optimizing stencil computations with hybrid tiling approaches are performed to obtain the advantages of concurrent start, load balancing, optimal data locality and good concurrency. Grosser et al. [68] develop a hybrid hexagonal/diamond tiling

approach, which can be used efficiently on GPUs. The hybrid tiling approach tiles the time dimension and outer spatial dimension into hexagonal tile shapes with diamond tiling along the other spatial dimensions. It involves no redundant computations and enables reuse along the time dimension while ensuring adequate parallelism.

# **Other Optimizations**

In addition to the tiling approaches, some work also focus on processor-level optimization. Dursun et al. [69] emphasize processor-level optimization techniques in their work. They propose a hierarchical scalable parallelization scheme, which efficiently uses the hierarchical memory levels in Intel multicore CPUs. Similarly, optimization works like tuning memory resources and overlapping memory transaction latency with operations are also performed on GPUs [70, 71, 44]

# CHAPTER 5 OPTIMIZING HIGHER-DIMENSIONAL DOACROSS PARALLELISM

Optimizing DOACROSS parallelism on GPUs is challenging because of the inherently sequential relationship and irregular workload across sub-problems. This is especially the case for higher-dimensional problems, those with three or more dimensions, where dimensionality refers to the number of loops for the nested loop. In this chapter, we present techniques to optimize performance for higher-dimensional DOACROSS parallelism on GPUs. We obtain the DOACROSS parallelism from a higher-dimensional dynamic programming procedure, which has a structured data access pattern. The dynamic programming procedure is obtained from the best existing polynomial-time approximation scheme for the problem of scheduling jobs on identical parallel machines. We demonstrate that the proposed technique highly optimizes the higher-dimensional dynamic programming procedure on GPUs and experimental results show that the optimized GPU implementation outperforms an optimized OpenMP implementation.

#### 5.1 Introduction

We study the optimization for the higher-dimensional DOACROSS parallelism for the problem of scheduling jobs on parallel identical machines to minimize makespan. The algorithm used to solve the problem is a Polynomial Time Approximation Scheme (PTAS) based on a higher-dimensional dynamic programming approach, where dimensionality refers to the number of variables in the dynamic programming equation characterizing the problem. Because the dynamic programming procedure accesses structured dependent data across multiple dimensions in each iteration, parallelizing the dynamic programming procedure leads to a regular DOACROSS parallelism and optimizing this procedure pro-

vides us with insight for optimizing higher-dimensional DOACROSS parallelism.

Although algorithms for several dynamic programming problems have already been ported to the GPU, challenges still remain, specially for higher-dimensional cases. In this study, the dimensionality refers to the number of variables in the dynamic programming equation characterizing the problems. Dynamic programming solutions are built from the solutions to sub-problems limiting the degree of parallelism that can be exploited. Furthermore, the workload imbalance among sub-problems increases with the number of dimensions. In addition, solving higher-dimensional dynamic programming problems can quickly exceed the GPU memory.

We consider higher-dimensional dynamic programming algorithms, those of three or more dimensions, and develop techniques to achieve an efficient implementation on the GPU. The proposed techniques resolve the memory issue and improve the thread-level workload balance. To illustrate the challenges and evaluate our techniques, we port to the GPU an approximation algorithm for scheduling jobs on identical parallel machines. This algorithm is a Polynomial Time Approximation Scheme (PTAS) based on an exact higher-dimensional dynamic programming approach. Our evaluation on the GPU considers as many as nine dimensions in order to assess the optimal decomposition of the various problem instances. We compare the performance of our GPU implementation with that obtained by an OpenMP implementation on a multicore CPU. The results show that our proposed tiling-like technique yields an efficient GPU algorithm with better performance on large problem instances, while also addressing the GPU memory limitations.

# 5.2 Tiling-Like Data-Partitioning Scheme

Even if the availability of the many cores on the GPU makes it possible to complete the massive calculations of a higher-dimensional dynamic programming (*DP*) problem in a relatively short time, the large storage requirement is still a challenge to GPU implementations. In the higher-dimensional *DP* problem, it is possible that each subproblem in the *DP-table* requires a big chunk of memory for temporarily holding the data of its dependent subproblems, so that even the execution of a relatively small size *DP* problem can also run out of memory. In this study, we resolve this issue by dividing the huge *DP-table* into many small blocks and performing executions on a number of blocks concurrently. Thus, we can save the memory usage by allocating memory only to the subproblems of these blocks. Here, we call the scheme of dividing the *DP* table, data-partitioning.

We now describe the idea of our proposed data-partitioning scheme for higher-dimensional *DP*. From a geometrical point of view, the partitioning evenly divides a multi-dimensional *DP-table* into multiple small blocks of the same size. The number of small blocks and the size of each block is determined by a vector, which we call *divisor*. A *divisor* has the same number of dimensions as the multi-dimensional *DP-table*, and the value on each dimension represents the number of segments that this dimension is divided into. Since the subproblems of the higher-dimensional *DP-table* are stored in row-major order, the subproblems of each small block are stored dispersedly in the array of the *DP-table*. Thus, from the data storage point of view, the partitioning scheme reorganizes the storage order of the array to have the subproblems stored within the small blocks.

In the parallel *DP* problems considered in this chapter, the flow of computation moves

along the main diagonal, and the subproblems on each anti-diagonal are independent. Thus, the subproblems on the same anti-diagonal can be processed in parallel (as shown in Fig. 5). In a partitioned *DP-table*, we develop the same computation flow and parallelization on the blocks and the subproblems in each block separately. In other words, our implementation first processes the blocks on the same level in parallel and then parallelize the subproblems on the same in-block anti-diagonal level.

As an example, let us consider a 3-dimensional  $DP\text{-}table\ (M,N,L)$  which is evenly divided by a  $divisor,\ (a,b,c)$ , and each small block can be represented by a vector (i,j,k), where  $i\leq a,\ j\leq b$ , and  $k\leq c$ . Thus, these blocks can be classified into different block-levels, and the vector indicates the block-level l=i+j+k that a block belongs to. Here, the term "block-level" refers to the blocks that can be executed concurrently, which is similar to the term "anti-diagonal level" for concurrent subproblems. We can also index each small block with a unique value, which is calculated from  $i\times b\times c+j\times c+k$ , so that these small blocks can be stored in a sequence with the index. In addition, a subproblem, represented by (x,y,z), belongs to the small block (i,j,k) if  $x\in\left[\frac{M\times i}{a},\frac{M\times (i+1)}{a}\right],\ y\in\left[\frac{N\times j}{b},\frac{N\times (j+1)}{b}\right]$ , and  $z\in\left[\frac{L\times k}{c},\frac{L\times (k+1)}{c}\right]$ . Moreover, we can indicate the subproblem's in-block anti-diagonal level (l=x+y+z) and calculate the vector (i,j,k) of the block it belongs to, where  $i=\lfloor x/\frac{M}{a}\rfloor,\ j=\lfloor y/\frac{N}{b}\rfloor$ , and  $k=\lfloor z/\frac{L}{c}\rfloor$ . All the subproblems (x,y,z) that belong to a small block (i,j,k) are stored consecutively in row-major order.

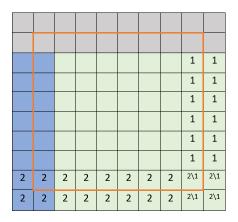

Fig. 4 shows an example of the data-partitioning scheme for a 3-dimensional *DP-table*. The table consists of  $6 \times 6 \times 6$  subproblems which are represented by the small cubes. Like the anti-diagonal parallelism in the 2-dimensional *DP-table*, shown in Fig. 5, the addition of the vector values indicates the anti-diagonal level the subproblems belongs to. Thus, the

Figure 4: Partitioning a 3-D *DP-table* by a divisor (3,3,3).

smallest subproblem (0,0,0) is in the first anti-diagonal level, and the largest subproblem (5,5,5) is in the 15th level. After partitioning the *DP-table* with the *divior*, all the subproblems are classified into multiple 3-dimensional blocks with a block size of  $2 \times 2 \times 2$ . Then, these blocks are also grouped into 7 different block-levels which are represented by 7 different colors, and the blocks with the same color are independent and can be executed concurrently. In addition, 8 subproblems, in each block, are also classified into 4 anti-diagonal levels, so that the in-block execution concurrency can also be obtained.

More details of the data-partitioning scheme are given in Section 5.4 where we employ the proposed techniques to a case study consisting of the PTAS algorithm for scheduling parallel identical machines. We will present the implementation of the dynamic programming procedure of the parallel version of PTAS on the GPU and analyze the advantages of using the data-partitioning scheme for resolving the problem efficiently. The blocklevel is indicated by l=i+j+k. Also, the index of the block can be calculated from  $i \times N \times L + j \times L + k$ . In addition, a configuration (x,y,z) belongs to the block (i,j,k) if

## **Algorithm 1** PTAS for $P||C_{max}$ by Hochbaum and Shmoys [15]

```

1: Input: n, m, \mathcal{T} = \{t_1, ..., t_n\}, \epsilon

2: LB \leftarrow \max \left\{ \left\lceil \frac{1}{m} \sum_{j=1}^{n} t_j \right\rceil, \max_{j=1,\dots,n} t_j \right\}

3: UB \leftarrow \left\lceil \frac{1}{m} \sum_{j=1}^{n} t_j \right\rceil + \max_{j=1,\dots,n} t_j

4: k = \lceil 1/\epsilon \rceil

5: while LB < UB do

T = |(UB + LB)/2|

Partition jobs into short and long jobs

7:

Round down long jobs to their nearest multiples of |T/k^2|

8:

OPT = DP(N, T)

9:

Obtain the schedule for rounded down long job sizes

10:

if OPT \leq m then

11:

UB = T

12:

else

13:

LB = T + 1

14:

15: Return the schedule

```

$$x \in \left[\frac{M \times i}{3}, \frac{M \times (i+1)}{3}\right]$$

,  $y \in \left[\frac{N \times j}{3}, \frac{N \times (j+1)}{3}\right]$ , and  $z \in \left[\frac{L \times k}{3}, \frac{L \times (k+1)}{3}\right]$ .

# 5.3 Dynamic Programming in the Parallel PTAS

We illustrate our proposed techniques on a case study consisting of a parallel approximation algorithm for the problem of scheduling jobs on parallel identical machines to minimize makespan (denoted by  $P \mid\mid C_{max}$ ) proposed by Ghalami and Grosu [14]. Their parallel algorithm requires solving a higher-dimensional dynamic programming problem and is based on parallelizing the PTAS by Hochbaum and Shmoys [15]. In what follows, we call the algorithm presented in [14], the *parallel PTAS*. The basic idea of the PTAS is to partition the set of jobs into two sets, long and short jobs, round down the processing times of the long jobs, and find an optimal schedule for the rounded long jobs using the dynamic programming procedure. The parallelization of the dynamic programming procedure is the core of the *parallel PTAS*.

We now briefly describe the PTAS, presented in Algorithm 1. The algorithm requires as

Figure 5: Dependency graph for OPT(2,3)

input, the number of machines, m; the number of jobs, n; the processing times of the jobs  $t_i$ ,  $i=1,\ldots,n$ ; and the relative error  $\epsilon>0$ . We denote by  $\mathcal T$  the multiset of jobs' processing times, i.e.,  $\mathcal T=\{t_1,\ldots,t_n\}$ , and assume that all jobs' processing times are positive integers. The algorithm starts by computing the lower and upper bounds (denoted by LB and UB) on the optimal makespan of the set of n jobs on m identical machines (Lines 2-3).

The algorithm performs a bisection search procedure for a target makespan value T on the interval [LB, UB] and determines a schedule for the long jobs that fits within T. Next, it rounds down the processing times of the long jobs to their nearest multiples of  $\lfloor T/k^2 \rfloor$ , so that long jobs are classified into  $k^2$  dimensions, where  $k = \lceil 1/\epsilon \rceil$ . Then, the algorithm determines the number of jobs of each of the rounded sizes and creates a  $k^2$ -dimensional vector  $N = (n_1, \ldots, n_{k^2})$ , where  $n_i$  is the number of rounded long jobs. After creating the vector N, the algorithm finds a schedule for the long rounded jobs with a makespan within time T. This is done by employing the DP algorithm which determines the suitable

number of machines to achieve a makespan within T. The DP algorithm generates the set C of all possible machine configurations. A machine configuration is a  $k^2$ -dimensional vector  $(s_1, \ldots, s_{k^2})$  specifying an assignment of tasks to one machine and satisfying that the total rounded time is within T. The recurrence equation of the DP is given by

$$OPT(n_1, ..., n_{k^2}) =$$

$$1 + \min_{(s_1, ..., s_{k^2}) \in \mathcal{C}} OPT(n_1 - s_1, ..., n_{k^2} - s_{k^2}).$$

(5.1)

where  $OPT(n_1,\ldots,n_{k^2})$  is the minimum number of machines sufficient to schedule the set of jobs given by the vector N and leading to a makespan within T. The idea behind this recurrence is that a schedule assigns some jobs to one machine and then assigns the rest of the jobs to as few machines as possible. It is important to observe that each entry requires at most  $\lfloor 1/\epsilon \rfloor^{k^2}$  time to compute, and that the total number of entries is  $n^{k^2}$  Hence, the values of  $OPT(n_1,\ldots,n_{k^2})$  are the components of a dynamic programming table. Since  $k^2$  is greater than 3, the DP procedure falls within the higher-dimensional dynamic programming. The dynamic programming formulation (Equation 5.1) also implies that the subproblems at each level depend on subproblems at more than one previous level. These subproblems correspond to the components of a table which we call the DP-table. Figure 5 shows the assignment of the subproblems for the example of a two-dimensional DP-table to a parallel system composed of four cores.

The dynamic programming formulation (Equation 5.1) of the PTAS is *non-serial monadic*, which means that there is a single recursive term in the dynamic programming formulation and the subproblems at each level depend on subproblems at more than one previous level. These subproblems correspond to the components of a table which we call the *DP-table*.

## **Algorithm 2** *Parallel* DP(N,T) by Ghalami and Grosu [14]

```

1: Input: N = (n_1, \dots, n_{k^2}), T

2: \sigma \leftarrow (n_1 + 1)(n_2 + 1) \dots (n_{k^2} + 1)

3: Let v^i = (v^i_1, \dots, v^i_{k^2}) and OPT(v^i_1, \dots, v^i_{k^2}) be the i-th entry of DP-table in row-major order,

where i = 0, \ldots, \sigma - 1

4: parallel for i = 0, \ldots, \sigma - 1 do

5:

d_i = 0

for j = 0, ..., k^2 - 1 do

6:

d_i = d_i + v_i^i

7:

8: end parallel for

9: n' = n_1 + \ldots + n_{k^2}

10: for l = 0, ..., n' do

parallel for i = 0, \dots, \sigma - 1 do

11:

12:

if d_i = l then

if i = 0 then

13:

OPT(0,\ldots,0) \leftarrow 0

14:

break

15:

16:

\mathcal{O}_{v^i} \leftarrow \emptyset

C_{v^i} \leftarrow \text{all machine configurations of vector } v^i

17:

18:

for all (s_1,\ldots,s_{k^2})\in\mathcal{C}_{v^i} do

\mathcal{O}_{v^i} \leftarrow \mathcal{O}_{v^i} \cup \{OPT(v_1^i - s_1, \dots, v_{k^2}^i - s_{k^2})\}

19:

min \leftarrow \infty

20:

21:

for all o \in \mathcal{O}_{v^i} do

if min > o then

22:

min = o

23:

OPT(v_1^i, \dots, v_{k^2}^i) \leftarrow min + 1

24:

end parallel for

25:

26: return OPT(n_1, ..., n_{k^2})

```

The major contribution of the parallel PTAS algorithm [14] is related to the *DP*, which is based on two important characteristics of the computation of subproblems. First, the flow of computation moves along the main diagonal, and second, the subproblems on each anti-diagonal (denoted by Level x, in Figure 5) are independent. Thus, the subproblems on an anti-diagonal can be processed in parallel. Figure 5 shows the assignment of the subproblems for the example of a two-dimensional *DP-table* to a parallel system composed of four cores.

The parallelization of the higher-dimensional DP is presented in Algorithm 2. The

goal of the algorithm is to fill out the entire higher-dimensional *DP-table*. and find the optimal value of OPT(N). First, the algorithm determines the size of the DP-table,  $\sigma =$  $\prod_{i=1}^{k^2} (n_i + 1)$  (Line 2). Next, the P processors compute the sums of the distances of the vectors  $v^i, i=1,\ldots,\sigma$  in parallel (Lines 4-8). Because of the dependencies between the anti-diagonals, the parallel DP algorithm consists of n' + 1 sequential iterations, where n' is the number of long jobs. The subproblems on each level l (corresponding to antidiagonal l) can be identified by the same  $d_i$  value (Line 12) and executed by P processors in parallel (Lines 11-25). For computing the optimal value of a subproblem, we need to know its dependencies on the preceding subproblems and use them in Equation (5.1). Therefore, the algorithm generates the set  $C_{v^i}$  of all possible machine configurations,  $(s_1, \ldots, s_{k^2})$ , for vector  $v^i$  (Line 17). Next, the algorithm finds the location of all subproblems by searching the entire *DP-table* and reads their optimal values  $OPT(v_1^i-s_1,\ldots,v_{k^2}^i-s_{k^2})$ . Then, it places the values into multiset  $\mathcal{O}_{v^i}$  (Lines 18-19) and determines the minimum among all values of the subproblems currently in  $\mathcal{O}_{v^i}$ , adds 1 to the minimum and assigns the value to subproblem  $OPT(v_1^i,\ldots,v_{k^2}^i)$  (Lines 20-25). The ordering of iterations guarantees that at each level the algorithm already computed all the needed preceding subproblems.

# 5.4 GPU Implementation and Analysis

Since the *DP* procedure is the most expensive component of the PTAS in terms of running time, the parallelization of the *DP* algorithm becomes the major component of our GPU implementation. A straightforward port of the OpenMP implementation of the PTAS [14] to the GPU is inefficient, being about a hundred times slower than the OpenMP implementation. Thus, sophisticated designs using customized techniques are necessary

#### **Algorithm 3** GPU implementation of the PTAS

```

1: Input: n, m, \mathcal{T} = \{t_1, ..., t_n\}, \epsilon, proc = 4, dim \in \{3, ..., 9\}

2: L\hat{B}_p \leftarrow \frac{p}{proc} \max\left\{\left\lceil \frac{1}{m} \sum_{j=1}^n t_j\right\rceil, \max_{j=1,\dots,n} t_j\right\}, p=0,\dots,3

3: UB_p \leftarrow LB_{p+1}, p = 0, ..., 2

4: UB_{proc-1} \leftarrow \left\lceil \frac{1}{m} \sum_{j=1}^{n} t_j \right\rceil + \max_{j=1,\dots,n} t_j

5: k = \lceil 1/\epsilon \rceil, LB = LB_0, UB = UB_{proc-1}, count = 0

6: while LB < UB do

for p = 0, ..., proc - 1 do

7:

8:

T_p = \lfloor (UB_p + LB_p)/2 \rfloor

Partition jobs into short and long jobs

9:

Round down long jobs to nearest multiples of |T/k^2|

10:

Create a k^2-dimensional vector N=(n_1,...,n_{k^2})

11:

OPT_p = Partition(N, T_p, dim, p)

12:

13:

for i = 0, ..., proc - 1 do

if OPT_0 \leq m then

14:

UB = T_0

15:

LB = LB

16:

OPT = OPT_0

17:

else if OPT_{proc-1} > m then

18:

UB = UB

19:

20:

LB = T_{proc-1}

OPT = OPT_{proc-1}

21:

else if OPT_i > m and OPT_{i+1} \leq m then

22:

23:

UB = T_{i+1}

LB = T_i

24:

OPT = OPT_{i+1}

25:

26:

OPT \ Array[count] = OPT

count \leftarrow count + 1

27:

```

for achieving good performance on the GPU. Our GPU implementation of the PTAS and the higher-dimensional *DP* procedure are illustrated in Algorithms 3, 5, and 4.

The GPU PTAS is designed similarly as in Algorithm 1 and differentiated by the distinct execution scopes. In the GPU implementation of PTAS, presented in Algorithm 3, the [LB,UB] interval is equally divided into four independent segments. The bisection search and the DP procedure is executed concurrently on each of these segments. Algorithm 5 presents the procedure for partitioning the higher-dimensional DP-table and the memory restructuring. Algorithm 4 shows the implementation of the higher-dimensional DP pro-

cedure and the work distribution which is designed for achieving the maximum execution concurrency.

In the rest of the chapter, we will use the term 'configuration' to refer to a subproblem of the higher-dimensional dynamic programming.

# 5.4.1 Design and Challenges