Wayne State University

Wayne State University Dissertations

January 2020

# Improved Contacts And Device Performance In Mos2 Transistors Using 2d Semiconductor Interlayers

Kraig Andrews Wayne State University

Follow this and additional works at: https://digitalcommons.wayne.edu/oa\_dissertations Part of the Electrical and Computer Engineering Commons, Nanoscience and Nanotechnology Commons, and the Physics Commons

### **Recommended Citation**

Andrews, Kraig, "Improved Contacts And Device Performance In Mos2 Transistors Using 2d Semiconductor Interlayers" (2020). *Wayne State University Dissertations*. 2343. https://digitalcommons.wayne.edu/oa\_dissertations/2343

This Open Access Dissertation is brought to you for free and open access by DigitalCommons@WayneState. It has been accepted for inclusion in Wayne State University Dissertations by an authorized administrator of DigitalCommons@WayneState.

## IMPROVED CONTACTS AND DEVICE PERFORMANCE IN MoS<sub>2</sub> TRANSISTORS USING 2D SEMICONDUCTOR INTERLAYERS

by

### **KRAIG ANDREWS**

### DISSERTATION

Submitted to the Graduate School

of Wayne State University,

Detroit, Michigan

in partial fulfillment of the requirements

for the degree of

## DOCTOR OF PHILOSOPHY

2020

MAJOR: PHYSICS

Approved By:

Advisor

Date

## DEDICATION

To my family, friends, and everyone who has provided support along the way

"The fact that we live at the bottom of a deep gravity well, on the surface of a gas covered planet going around a nuclear fireball 90 million miles away and think this be normal is obviously some indication of how skewed our perspective tends to be."

-Douglas Adams

#### ACKNOWLEDGEMENTS

First and foremost, I would like to thank my advisor, Dr. Zhixian Zhou, for all the guidance and support he has provided throughout this endeavor. Dr. Zhou embodies an ideal Ph.D. advisor. It was truly a privilege to learn from him and his immense wealth of knowledge. His enthusiasm, encouragement, and perpetual patience keep me confident and motivated. It was truly a rewarding experience to work with him. I would also like to thank my dissertation committee: Dr. Jian Huang, Dr. Ashis Mukhopadhyay, and Dr. Ming-Cheng Cheng. Their insightful comments and suggestions during this entire process have strengthened this work, lending to their broad knowledge and research perspectives.

I owe a great debt of gratitude to all the group members of the Nanofabrication and Electron Transport Laboratory, past and present, who contributed to my experiment work and engaged in helpful scientific discussions. I specifically would like to thank Dr. Hsun-Jen Chuang, Dr. Meeghage Madusanka Perera, and Dr. Bhim Chamlagain who helped considerably in the early days of my Ph.D work and taught me many of the 2D fabrication and processing techniques presented in this work. I also would like thank Arthur Bowman III, his cooperation, assistance, and advice throughout these years have been indispensable to the completion of this work. The help of Dr. Ehab Abdelhamid and the many hours troubleshooting different toolsets are not forgotten. Many other colleagues and friends, such as Dr. Parisa Bashiri, Dr. Qingsong Cui, Dr. Nick Elsey, Dr. Xinxin Woodward, Zhiguo Zhao, Gui Chen, and Liang Zhu from the Wayne State Department of Physics and Astronomy and Department of Electrical and Computer Engineering throughout the years have been greatly appreciated and not forgotten.

iii

The completion of my Ph.D. and this work would not have been possible without my research collaborators. Dr. Yaqoing Xu at Vanderbilt University and her research students, Tianjiao Wang and Thayer Walmsley, with whom we worked on several research projects. Their optical measurements were vital to understanding many of our mutual projects and their suggestions were always helpful. Dr. David Mandrus at The University of Tennessee, Knoxville and his research students, Dr. Michael Koehler and Amanda Haglund, who grew and provided many of materials used in this work. Dr. Pai-Yen Chen at the University of Illinois at Chicago and his research student Liang Zhu for their theoretical simulations and lively discussions that provided direction and strengthened our work.

The bulk of the fabrication and processing work during my Ph.D. occurred at nFab at the Wayne State University Electrical and Computer Engineering Department and, later, at Lurie Nanofabrication Facility (LNF) at the University of Michigan. Dr. Daniel Dursin and Dr. William Funk at nFab were very helpful in teaching me basic semiconductor processing techniques. Dr. Sandrine Martin, Dr. Pilar Herrera-Fierro, Dr. Vishva Ray, and Dr. Matt Oonk at LNF were supportive in sharing their respective knowledge in troubleshooting processes and tool operations.

My summer internship at the National Institute of Materials Science at the International Center for Materials Nanoarchitectonics in Tsukuba, Japan facilitated by Dr. Kazuhito Tsukagoshi, taught me many valuable skills and tools that I still use to this day.

In particular I would like to thank the very generous support of Dr. Jim Kaskas and the Dr. Jim Kaskas Scholarship Fund whose generous support made this work possible, I am truly grateful for his kindness and support of my work. The Frank Knoller Endowed

iv

Fellowship in Physics has also provided wonderful support, allowing me to finish my Ph.D. work. Furthermore, the support of the Wayne State Department of Physics and Astronomy has been crucial to my success over these years.

Last, but certainly not least, I would like to thank my friends and family for their unwavering support during these years. Without their guidance and backing, none of this would have been possible.

| DEDICATIC   | DNii                                                           |

|-------------|----------------------------------------------------------------|

| ACKNOWL     | EDGEMENTSiii                                                   |

| LIST OF TA  | BLESx                                                          |

| LIST OF FIG | GURESxi                                                        |

| LIST OF AE  | BREVIATIONS                                                    |

| Chapter 1 E | BACKGROUND AND MOTIVATION1                                     |

| 1.1 Fiel    | d-Effect Transistors1                                          |

| 1.2 Two     | o-Dimensional Materials and Transition Metal Dichalcogenides10 |

| 1.3 Cha     | allenges in Two-Dimensional Electronics                        |

| 1.4 Cor     | ntact Approaches in Two-Dimensional Electronics                |

| 1.4.1       | Phase Engineering 17                                           |

| 1.4.2       | Chemical Doping                                                |

| 1.4.3       | Insulating Interlayer Contacts                                 |

| 1.4.4       | Semiconducting Interlayer Contacts                             |

| 1.5 Scc     | ppe of the Dissertation                                        |

| Chapter 2 [ | DEVICE FABRICATION AND CHARACTERIZATION                        |

| 2.1 Mea     | chanical Exfoliation of 2D Materials and TMDs24                |

| 2.1.1       | Substrate Preparation and Cleaning25                           |

| 2.1.2       | Mechanical Exfoliation                                         |

## TABLE OF CONTENTS

| 2.2    | van der Waals Assembly of 2D Materials and TMDs                                   | 31 |

|--------|-----------------------------------------------------------------------------------|----|

| 2.2    | .1 Dry Pickup Method                                                              | 31 |

| 2.3    | Electron Beam Lithography                                                         | 34 |

| 2.4    | Metal Deposition                                                                  | 38 |

| 2.5    | Liftoff                                                                           | 40 |

| 2.6    | Annealing                                                                         | 41 |

| 2.7    | Device Characterization                                                           | 42 |

| 2.7    | .1 Atomic Force Microscopy                                                        | 42 |

| 2.7    | 2.2 Electrical Measurements                                                       | 43 |

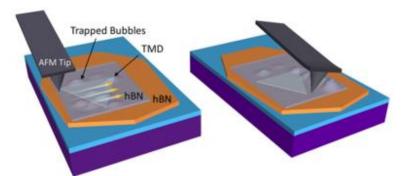

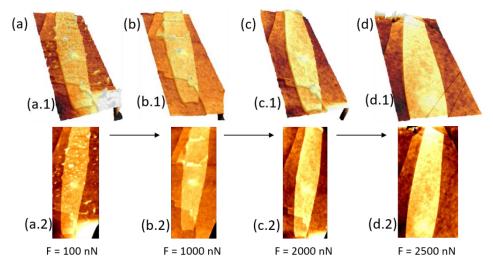

| 2.8    | Nano-Squeegee                                                                     | 45 |

| Chapte | er 3 CONTACT PROPERTIES OF 2D INTERLAYER FETs                                     | 48 |

| 3.1    | Introduction                                                                      | 48 |

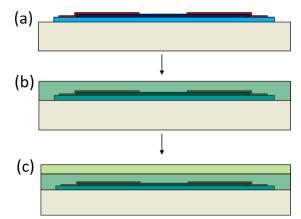

| 3.2    | Semiconductor Interlayer Contacts Device Fabrication                              | 52 |

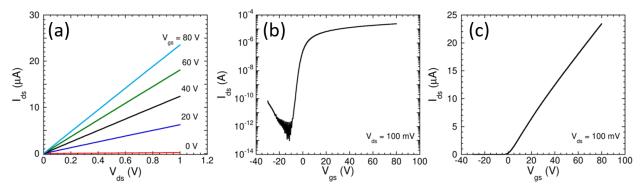

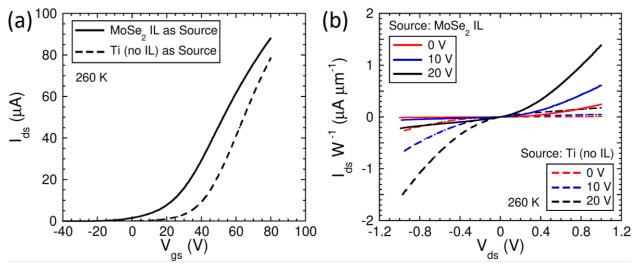

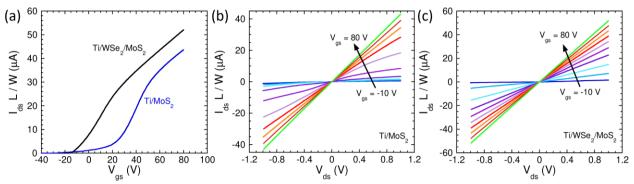

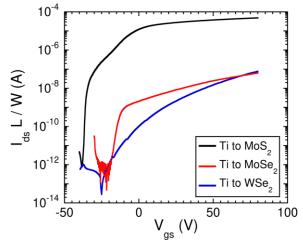

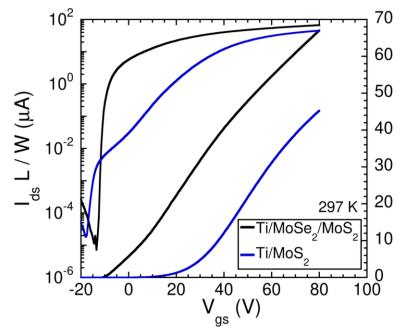

| 3.3    | Transfer Characteristics of MoS <sub>2</sub> Devices with Interlayers             | 53 |

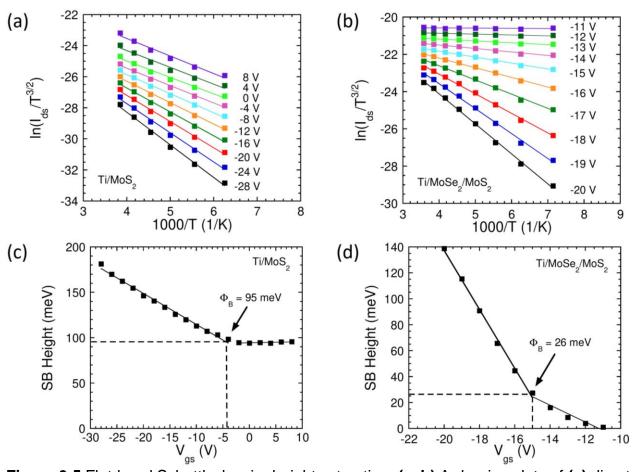

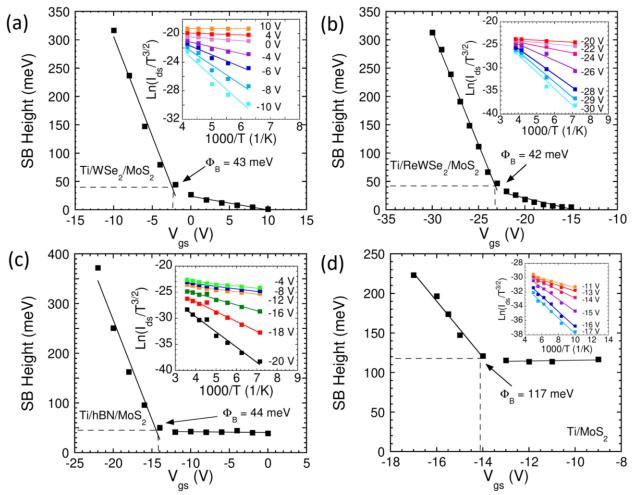

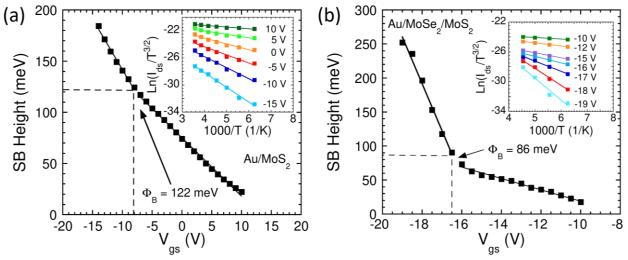

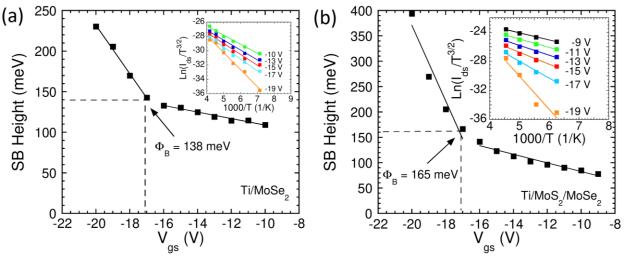

| 3.4    | Schottky Barrier Height Extraction                                                | 57 |

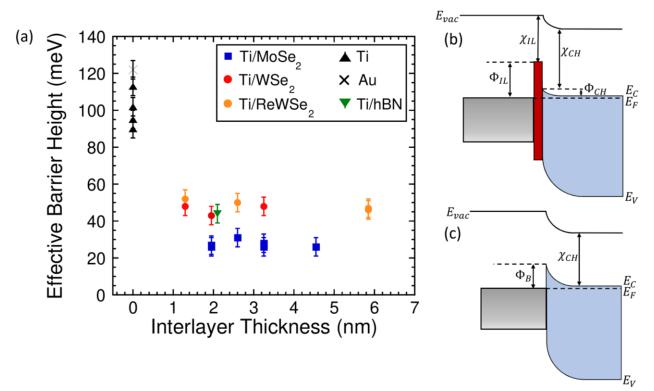

| 3.4    | .1 Schottky Barrier Height with Interlayer Contacts to MoS <sub>2</sub>           | 58 |

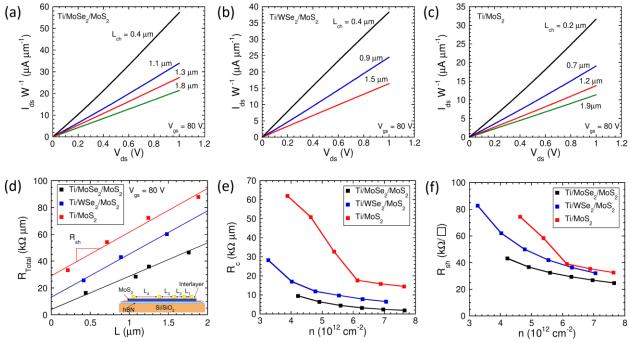

| 3.5    | Contact Resistance, Resistivity, and Transfer Length                              | 65 |

| 3.5    | 5.1 Evaluation of Contact Resistance in MoS <sub>2</sub> Devices with Interlayers | 65 |

| 3.5    | 2 Extraction of Contact Resistivity and Transfer Length                           | 67 |

| 3.5    | 3.3 Temperature Dependent Contact Properties                                      | 71 |

| 3.6    | Effects of Tunneling Barrier Height and Width                                    | 72      |

|--------|----------------------------------------------------------------------------------|---------|

| 3.7    | Contributions of Interlayer Conduction to Device Conduction                      | 74      |

| 3.8    | Summary                                                                          | 75      |

| Chapte | er 4 PERFORMANCE OF 2D INTERLAYER FETs                                           | 76      |

| 4.1    | Introduction                                                                     | 76      |

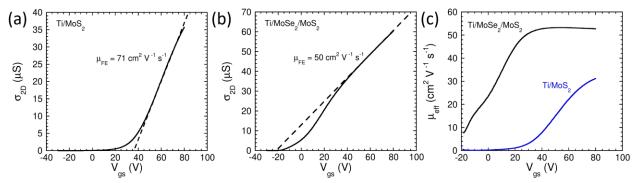

| 4.2    | Field-Effect and Effect Mobilities                                               | 77      |

| 4.2    | 2.1 Field-Effect Mobility                                                        | 77      |

| 4.2    | 2.2 Effective Mobility                                                           | 77      |

| 4.2    | 2.3 Comparison of Mobilities                                                     | 77      |

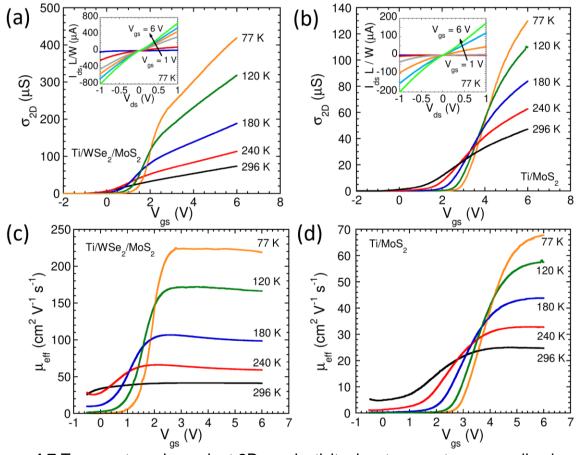

| 4.3    | Temperature Dependent Transfer Characteristics                                   |         |

| 4.4    | Characteristics of WSe <sub>2</sub> Interlayer Contacts to $MoS_2$ FETs with a G | raphite |

| Gate   | and hBN Dielectric                                                               |         |

| 4.5    | Improving the Subthreshold Swing                                                 | 91      |

| 4.6    | Characteristics of Hetero-Layer MoS <sub>2</sub> FETs                            |         |

| 4.7    | Summary                                                                          | 97      |

| Chapte | er 5 CONCLUSIONS AND FUTURE WORK                                                 |         |

| 5.1    | Conclusions                                                                      |         |

| 5.2    | Future Work                                                                      |         |

| REFEF  | RENCES                                                                           | 102     |

| ABSTR  | RACT                                                                             | 113     |

| 115 |

|-----|

|     |

## LIST OF TABLES

| Table 1.1 Device scaling rules for FETs.    5 |

|-----------------------------------------------|

|-----------------------------------------------|

**Table 1.2** Bandgaps of bulk and monolayer group VI TMD semiconductors. In parenthesisthe "I" or "D" indicates whether the bandgap is indirect or direct, respectively.13

## LIST OF FIGURES

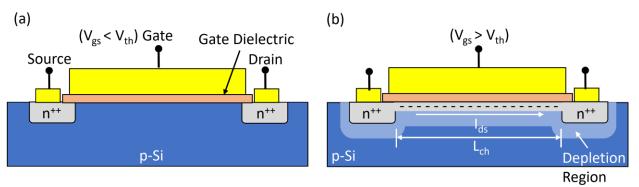

**Figure 1.2** Illustration of decreasing device geometry and its effects on operation. In a sufficiently (a) long channel device, operation occurs as normal. (b) When the device size begins to shrink, the depletion region size increases and a (c) further decrease in size yields a larger depletion region size. In each case, the threshold voltage may be altered due to DIBL and the device may turn on prematurely. (d) At the limit, the depletion regions at each contact merge and punch-through occurs rendering the device inoperable. ...... 6

**Figure 1.5** Energy band diagram for metal-semiconductor (n-type) contacts before and after being brought into contact. (a) In this case the metal work function  $\Phi_M$  is less than the semiconductor work function  $\Phi_S$ . The values of the electron affinity  $\chi$ ,  $\Phi_M$ , and  $\Phi_S$  are measured from the vacuum level  $E_o$ , the minimum energy needed to release an electron from the material. (b) The flat band diagram of metal-semiconductor contacts under equilibrium conditions, where the difference between the metal work function  $\Phi_M$  and the electron affinity of the semiconductor  $\chi$  yields the Schottky barrier height  $\Phi_B$  of the contacts.

**Figure 1.9** Insulating interlayer contacts to  $MoS_2$  FETs using metal oxides. **(a)** Schematic diagram of a  $MoS_2$  FET using  $Ta_2O_5$  inserted between the Ti/Au contacts and the  $MoS_2$  channel. Originally appeared in Lee et al., Nano Letters, (2015).<sup>64</sup> **(b)** Diagram of a  $MoS_2$  FET using TiO<sub>2</sub> interlayer contacts between  $MoS_2$  and Co contacts. Originally appeared in Dankert et al., ACS Nano, (2014).<sup>65</sup> **(c)** Illustration of a  $MoS_2$  using MgO between the Co contacts and  $MoS_2$  channel. Originally appeared in Chen et al., Nano Letters, (2013).<sup>66</sup>

**Figure 2.4** Heating exfoliation of 2D materials. **(a)** The exfoliated tape is placed on a clean SiO<sub>2</sub> substrate and **(b)** pressed continuously to remove and air traps. **(c)** The tape/substrate is placed crystal side down on the heating element for 5 minutes at 95°C,

**Figure 2.6** Steps involved in picking up a 2D flake from SiO<sub>2</sub> substrate. **(a)** The sample desired for pickup is **(b)** covered with PC film and **(c)** flattened over the sample. **(d)** A PDMS is cut and placed over the PC film and sample. **(e)** The excess PC film and PDMS is cut away and the PDMS/PC/sample is **(f)** picked up from the substrate and **(g)** put on a glass slide.

Figure 2.8 Scanning electron microscope (SEM) with electron beam attachment........ 35

| <b>Figure 2.10</b> Electron beam lithography (EBL) bi-layer resist application. <b>(a)</b> The finished device is first <b>(b)</b> coated with 495K PMMA and hard baked. Then a layer of <b>(c)</b> 950K PMMA is applied, followed by another hard bake |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.11 Example of bi-layer PMMA resist undercut                                                                                                                                                                                                    |

| Figure 2.12 Pattern development after electron beam lithography exposure                                                                                                                                                                                |

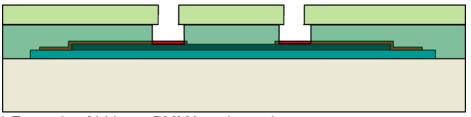

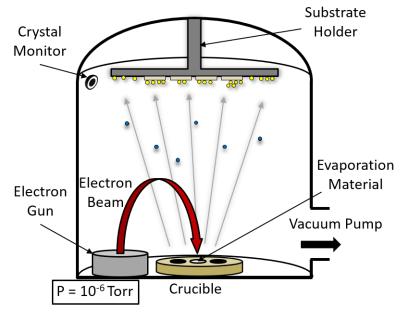

| Figure 2.13 Schematic illustration electron-beam assisted evaporation chamber 39                                                                                                                                                                        |

| Figure 2.14 Sample after deposition of Ti/Au 40                                                                                                                                                                                                         |

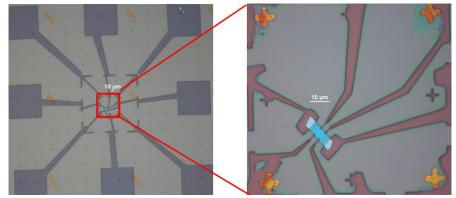

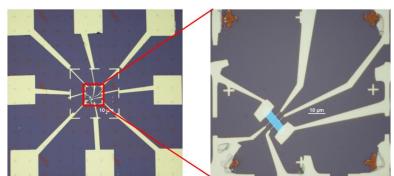

| Figure 2.15 Optical image of sample after liftoff, showing 10x and 100x magnification. 40                                                                                                                                                               |

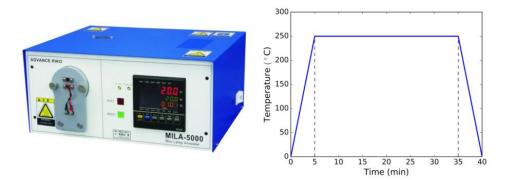

| Figure 2.16 (a) Vacuum annealing setup. (b) Temperature program for annealing devices                                                                                                                                                                   |

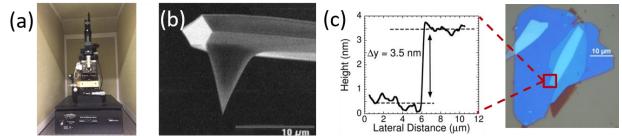

Figure 2.17 (a) Atomic force microscope (AFM) setup. (b) Magnified image of AFM tip. (c) Example line profile resulting from AFM scan on device to determine flake thicknesses. 43

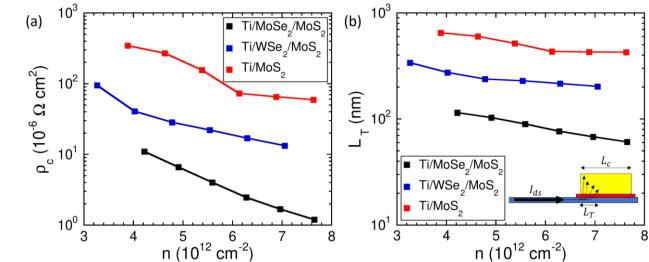

**Figure 3.11** Calculated specific contact resistivity and transfer length of MoS<sub>2</sub> FETs. (a) Specific contact resistivity and (b) transfer length as a function of carrier density

calculated from  $RC = \rho C/LT cothLC/LT$  and  $LT = \rho C/Rsh1/2$ , where Rc and R<sub>sh</sub> are extracted from the TLM measurements. The **inset** of **(b)** shows an illustration of the decaying current injected over the transfer length. In each contact type, the average contact length (Lc) was 1 µm which is at least several times large the largest transfer length, ensuring that current crowding is not a significant factor in our measurements. 69

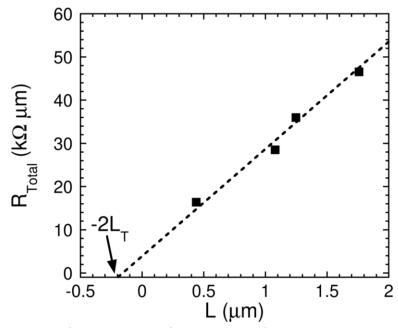

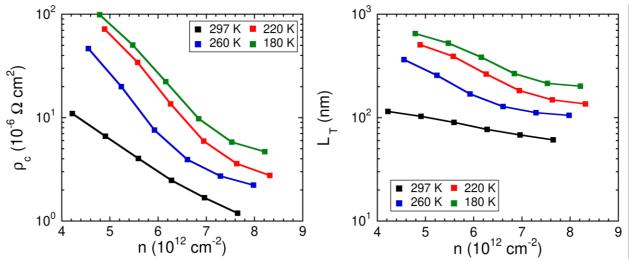

**Figure 3.13** Extracted **(a)** Specific contact resistivity and **(b)** transfer length as a function of carrier density at several different temperatures for Ti/MoSe<sub>2</sub> contacts to MoS<sub>2</sub>......72

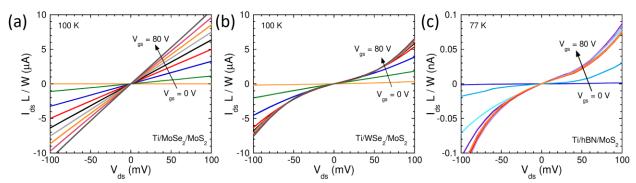

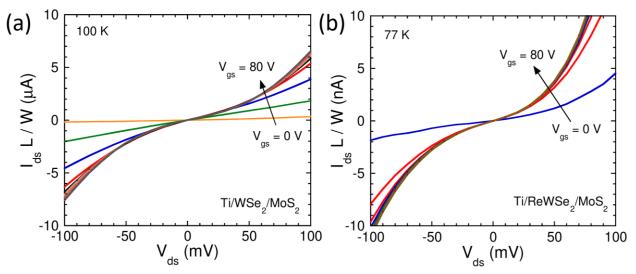

**Figure 3.15** Low temperature normalized output current for **(a)** Ti/WSe<sub>2</sub> and **(b)** Ti/ReWSe<sub>2</sub> (note the different unit of current) contacts to MoS<sub>2</sub> FETs......74

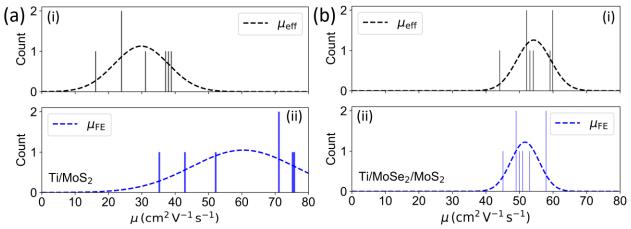

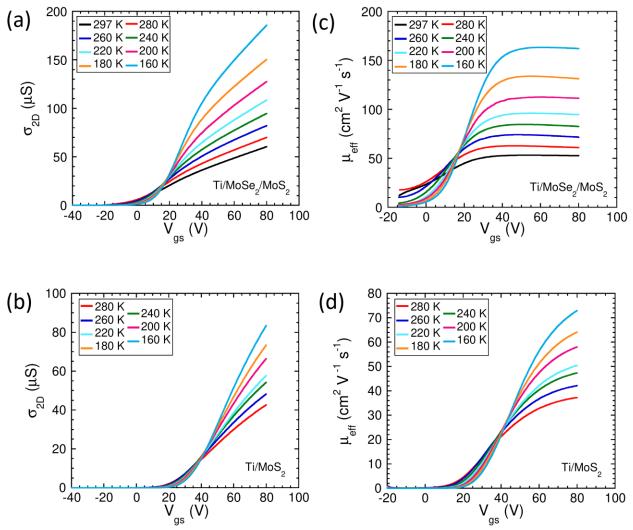

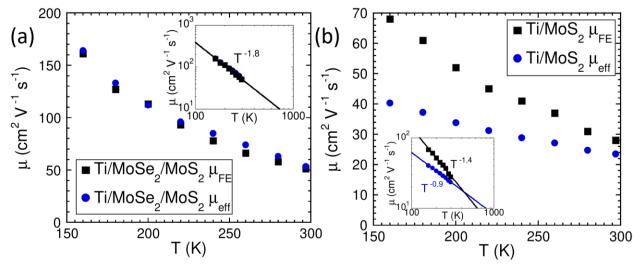

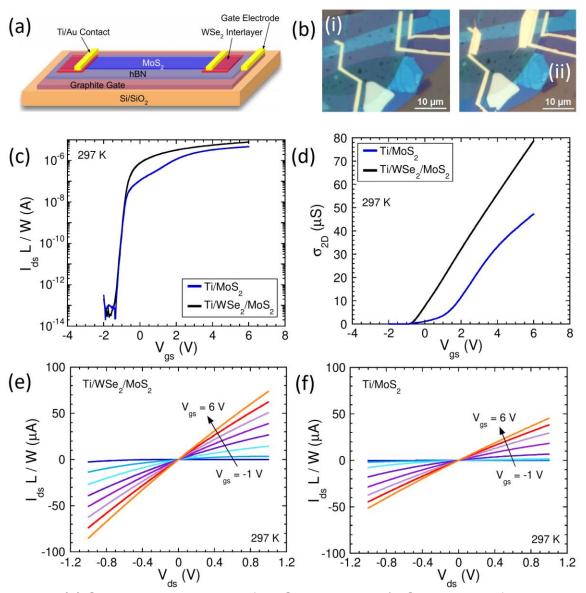

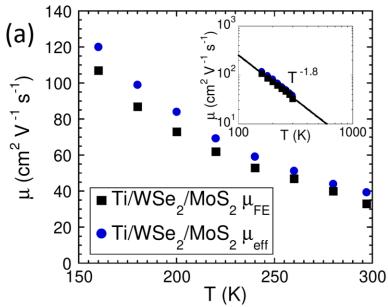

**Figure 4.5** Comparison of the field-effect ( $\mu FE$ ) and effective ( $\mu eff$ ) mobilities for decreasing temperatures at VGS = 80 V for **(a)** Ti/MoSe<sub>2</sub> and **(b)** direct Ti contacts to MoS<sub>2</sub>.

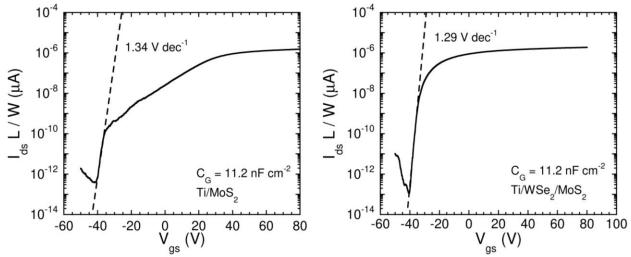

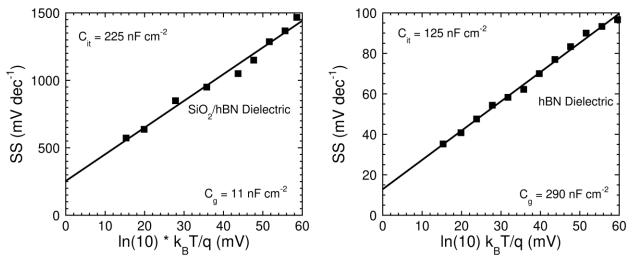

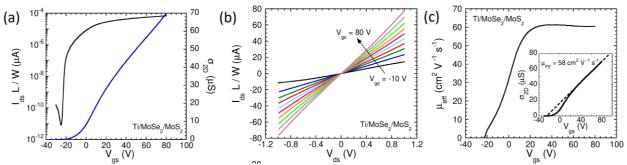

**Figure 4.9** Extraction of subthreshold swing (SS) at room temperature in MoS<sub>2</sub> FETs fabricated on a SiO<sub>2</sub>/hBN dielectric stack with **(a)** direct Ti and **(b)** Ti/WSe<sub>2</sub> contacts...92

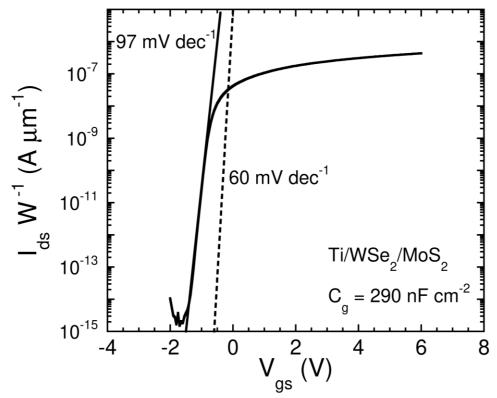

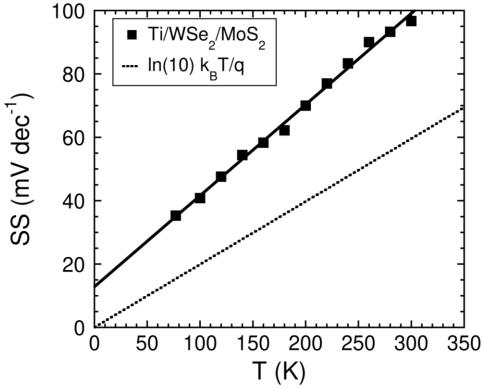

**Figure 4.11** SS as a function of temperature in a Ti/WSe<sub>2</sub> contacted MoS<sub>2</sub> using a hBN dielectric on a graphite gate. The dashed line shows the fundamental limit of SS. .......95

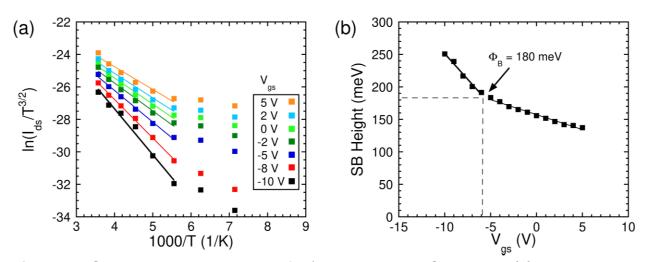

**Figure 5.1** Schottky barrier extraction of Ti/Au contacted PdSe<sub>2</sub> device. **(a)** The Arrhenius plots for several back-gate bias voltages measured with drain voltage bias at 100 mV. The slope of each curve yields the effective Schottky barrier height at the corresponding gate bias. **(b)** The extracted effective Schottky barrier height at the various back-gate bias voltage, where the flat-band electron Schottky barrier height is measured to be 180 meV.

## LIST OF ABBREVIATIONS

| 2D               | Two-Dimensional                         |

|------------------|-----------------------------------------|

| AFM              | Atomic Force Microscopy                 |

| ALD              | Atomic Layer Deposition                 |

| BEUV             | Beyond Extreme Ultraviolet              |

| BP               | Black Phosphorus                        |

| CMOS             | Complementary Metal-Oxide Semiconductor |

| CNL              | Charge Neutrality Level                 |

| CVD              | Chemical Vapor Deposition               |

| DIBL             | Drain Induced Barrier Lowering          |

| EBL              | Electron Beam Lithography               |

| EUV              | Extreme Ultraviolet                     |

| FET              | Field-Effect Transistor                 |

| FinFET           | Fin Field-Effect Transistor             |

| FLP              | Fermi Level Pinning                     |

| GAAFET           | Gate-All-Around Field-Effect Transistor |

| GaAs             | Gallium Arsenide                        |

| Ge               | Germanium                               |

| hBN              | Hexagonal Boron Nitride                 |

| HDMS             | Hexamethyldisilazane                    |

| HfO <sub>2</sub> | Hafnium Oxide                           |

| IC               | Integrated Circuit                      |

| IPA              | Isopropanol                             |

| MEK               | Methyl Ethyl Ketone               |

|-------------------|-----------------------------------|

| MgO               | Magnesium Oxide                   |

| MIBK              | Methyl Isobutyl Ketone            |

| MIGS              | Metal Induced Gap States          |

| MIS               | Metal-Insulator Semiconductor     |

| MoS <sub>2</sub>  | Molybdenum Disulfide              |

| MoSe <sub>2</sub> | Molybdenum Diselenide             |

| MoTe <sub>2</sub> | Molybdenum Ditelluride            |

| MSS               | Metal-Semiconductor-Semiconductor |

| nMOS              | n Metal-Oxide Semiconductor       |

| NPGS              | Nanopattern Generation System     |

| PC                | Polycarbonate                     |

| PDMS              | Polydimethylsiloxane              |

| PdSe <sub>2</sub> | Palladium Diselenide              |

| PEB               | Post-Exposure Bake                |

| РММА              | Polymethyl Methacrylate           |

| pMOS              | p Metal-Oxide Semiconductor       |

| PR                | Photoresist                       |

| PVD               | Physical Vapor Deposition         |

| SB                | Schottky Barrier                  |

| SBH               | Schottky Barrier Height           |

| SCE               | Short Channel Effect              |

| SEM               | Scanning Electron Microscope      |

|                   |                                   |

| Si                             | Silicon                                 |

|--------------------------------|-----------------------------------------|

| SiO <sub>2</sub>               | Silicon Oxide                           |

| SS                             | Subthreshold Swing                      |

| Ta <sub>2</sub> O <sub>5</sub> | Tantalum Oxide                          |

| TiO <sub>2</sub>               | Titanium Oxide                          |

| TLM                            | Transfer Length Method                  |

| TMD                            | Transition Metal Dichalcogenide         |

| UTB-FET                        | Ultra-Thin Body Field-Effect Transistor |

| UV                             | Ultraviolet                             |

| VdW                            | van der Waals                           |

| WS <sub>2</sub>                | Tungsten Disulfide                      |

| WSe <sub>2</sub>               | Tungsten Diselenide                     |

## **Chapter 1 BACKGROUND AND MOTIVATION**

#### 1.1 Field-Effect Transistors

Over the past half-century, integrated circuits (ICs) have revolutionized technology, playing a role in nearly all modern electronic devices. At the heart of an IC lies the field-effect transistor (FET). A FET is a three-terminal device consisting of a drain, source, and gate. A typical silicon (Si) FET is structure is fabricated on a substrate with heavily doped drain/source regions. A dielectric material (e.g. silicon oxide; SiO<sub>2</sub>, hafnium oxide; HfO<sub>2</sub>) is deposited or grown (SiO<sub>2</sub> is typically thermally grown while some other oxides like HfO<sub>2</sub> are deposited using atomic layer deposition) in the region of the substrate spanning the heavily doped drain and source. Metal is subsequently deposited over the drain/source regions as well as the dielectric material, functioning as the drain/source electrodes and the gate electrode, respectively. There are two types of basic Si-FETs: *n*- or *p*-Si FETs. Here, the discussion will focus on *n*-Si FETs (or nMOS), for *p*-Si FETs (or pMOS) the principle is the same, but the *n*- and *p*-doping is interchanged. For example, an *n*-Si FET is fabricated with a *p*-Si substrate and heavily *n*-doped drain/source regions as shown in *Figure 1.1*(a).

A FET operates based on two distinct electric fields. The transverse electric field develops as a result of the applied potential difference between the gate and the substrate, known as the gate voltage,  $V_{GS}$ . The lateral electric field arises due to the application of a non-zero source to drain potential,  $V_{DS}$ , and is the primary mechanism driving current flow in the FET. Consider a device initially in the off-state, where the gate-voltage is much less than the voltage needed to induce a channel (i.e. the threshold voltage),  $V_{GS} \ll V_{TH}$ , and a non-zero source/drain voltage,  $V_{DS} > 0$  (for *n*-Si FETs). In this

case, the drain and source regions form forward and reverse biased p-n junctions with the substrate preventing a substantial flow of current, contributing to low off-state current. When the gate voltage is increased, but still below the threshold voltage, the transverse electric field produced by the gate penetrates further into the substrate. This electric field repels majority holes (in the case of a p-Si substrate) from the surface, creating a depletion region near the surface. A portion of the depletion region is assisted by the drain/source p-n junctions, the depletion charge in the would-be channel region is balanced by charge in drain/source regions. In addition, some minority electrons are attracted to the surface, but at these low gate voltage values their concentrations are not enough to cause much effect. As the gate voltage is increased further, the transverse electric field continues to repel majority holes from the surface while attracting minority electrons to the surface. At some gate voltage value, the threshold voltage is reached where an inversion layer is formed. Here the inversion layer dominates over the intrinsic substrate doping levels. The inversion layer is a dense concentration of electrons that extends from the source to drain regions and forms the conductive channel of the FET as shown in *Figure 1.1(b)*. Once the threshold voltage is reached, the lateral electric field drives current flow from the source to drain and further increasing the gate voltage only increases the density of the inversion layer.

**Figure 1.1** Basic schematic of 3D FET and operation. (a) Schematic of nMOS device with heavily n-doped drain and source regions and gate dielectric in the off-state. (b) As the gate voltage is increased, the holes present near the surface are repelled by the application of a positive gate voltage (and its resulting electric field). Further application and increase in the gate voltage yields a depletion region beneath the contacts and a small concentration of electrons near the surface. Once the threshold voltage is reached, a conductive channel of electrons is formed that extends from the source and drain and defines the channel length over which current can flow.

The ICs used in digital, analog, and memory circuits require increasingly larger transistor density to enable low-power and high-speed devices. Until recently, Moore's observation that computing power doubles every two years has held and has been facilitated by large increases in the number of transistors.<sup>1</sup> To accommodate the need for larger densities, the FETs that compose the ICs have been increasingly miniaturized. In the 1970s transistor sizes were on the order of several microns with densities near one-hundred thousand transistors per chip.<sup>2, 3</sup> While in 2018, commercial transistor sizes had decreased substantially to less than ten nanometers and the densities had skyrocketed to well over a billion transistors per chip.<sup>4</sup> In less than 50 years the transistor size has decreased nearly three orders of magnitude while the density has increased by over five orders of magnitude.

Increasingly miniaturized devices come at a cost, however. Decreased transistor size requires increasingly complex fabrication processes, often requiring the development of new equipment and techniques to help facilitate these processes. For example, resolution in photolithography, an integral process in IC fabrication is limited by the diffraction limit. To reach resolutions adequate for the 10 nm technology node new techniques such as extreme ultraviolet (EUV) and beyond extreme ultraviolet (BEUV) lithography are being explored.<sup>5</sup> Aside from fabrication challenges, there are much more pressing issues in terms of the physical consequences of transistor scaling.

In order to properly scale devices, various FET parameters must be scaled simultaneously to ensure proper device function. Generally, this is to keep the internal electric fields constant.<sup>6</sup> As the device size is decreased, and the channel length transitions from the long-channel to the short-channel regime, the potential distribution in the channel begins to depend on both the x and y - directions. To mitigate this effect, the device parameters must be changed in concert with one another. For example, if the device length (L) is scaled by a factor of  $\kappa$ , then so should the device width (W), junction depths  $(x_i)$ , and oxide thickness  $(t_{ox})$ . **Table 1.1** summarizes some the scaling factors for FETs, known as Dennard scaling factors.<sup>7</sup> However, as device geometries have decreased substantially since the advent of these scaling rules it has been difficult and impractical to maintain them. The primary reason for this is that these ideal scaling rules are impeded by other factors that are fundamentally not scalable. Parameters like the channel doping  $(N_{A})$  cannot be scaled indefinitely without fear of p-n junction breakdown or the contact junction depth cannot be scaled indefinitely without sacrificing lowresistance at the contact interface.<sup>6</sup> If devices are not scaled properly, then issues begin to emerge that adversely affect device operation, known as short channel effects (SCEs).

| Device or Circuit Parameter             | Scaling Factor |

|-----------------------------------------|----------------|

| Device dimension $t_{ox}$ , L, W, $x_j$ | 1/κ            |

| Doping concentration Na                 | Κ              |

| Voltage V                               | 1/κ            |

| Current /            | 1/κ              |

|----------------------|------------------|

| Power dissipation VI | 1/κ <sup>2</sup> |

Table 1.1 Device scaling rules for FETs.

Suppose that in a short channel device, the channel thickness is not scaled properly (i.e. the scaling has not followed the rules laid out in **Table 1.1**), and the drain/source junction depths are too deep. This can cause unintended electrostatic interactions between the source and drain. The inversion and depletion layers are primarily created by the transverse electric field applied by the gate; however, the drain/source regions also work to balance some of the depletion charge. For long channel devices, the percentage of depletion charge balanced by the drain/source regions is small compared to the charge depletion induced by the gate. As the channel length is decreased, however, the drain/source regions balance a greater percentage of depletion charge. This effect, known as drain induced barrier lowering (DIBL), lowers the potential barrier to the channel and alters the threshold voltage of the device. Figure 1.2 shows the effect that decreasing device geometry has on the depletion region sizes at the drain and source. In the extreme case of DIBL, the depletion regions beneath the drain and source can merge, exhibiting a phenomenon known as punch-through, rendering the device inoperable. Obviously, alterations in the threshold voltage and other unintended SCEs are undesirable for reliable device operation. While there are some actions that can be taken to prevent DIBL, such as anti-punch-though implants, or reducing the drain/source junction depth, these still do not protect against SCEs indefinitely.<sup>3</sup> Structures or materials that can mitigate SCEs would be ideal while still maintaining the ability to miniaturize devices.

5

**Figure 1.2** Illustration of decreasing device geometry and its effects on operation. In a sufficiently (a) long channel device, operation occurs as normal. (b) When the device size begins to shrink, the depletion region size increases and a (c) further decrease in size yields a larger depletion region size. In each case, the threshold voltage may be altered due to DIBL and the device may turn on prematurely. (d) At the limit, the depletion regions at each contact merge and punch-through occurs rendering the device inoperable.

Since the breakdown of Dennard scaling and the deviation from the scaling rules, new device structures have been sought. This is a consequence of SCEs, as discussed above. Smaller device sizes result in a less electrostatic control. Control of device operation is governed by the potential distribution  $\Phi(x, y)$  in the channel, which according to Poisson's equation is given by

$$\frac{d^2\Phi(x,y)}{dx^2} + \frac{d^2\Phi(x,y)}{dy^2} = \frac{qN_A}{\epsilon_s},$$

(1.1)

where x is defined over the channel length ( $0 \le x \le L$ ) and y is defined over the channel thickness ( $0 \le y \le t_s$ ),  $N_A$  is the channel doping, and  $\epsilon_s$  is the dielectric constant of the channel material. Assuming the following boundary conditions: (i) the electric field at y =0 is determined by the capacitance of the gate, (ii) the electric field at  $y = t_s$  is essentially

6

zero, and (iii) the potential at the bottom of the channel is some constant function in the *x*-direction (i.e.  $\Phi(x, 0) = c_0(x)$ ).<sup>8</sup> It can be shown that **equation (1.1)** can be reduced to

$$\frac{d^2\Phi}{dx^2} = \frac{\Phi}{\lambda^2}.$$

(1.2)

The quantity  $\lambda$  is defined as the natural scaling length, and in a conventional FET design is defined as

$$\lambda = \sqrt{\frac{\epsilon_s}{\epsilon_{ox}} t_s t_{ox}},\tag{1.3}$$

where  $\epsilon_s$  and  $\epsilon_{ox}$  are the dielectric constants of the semiconductor and gate oxide material, respectively, and  $t_s$  and  $t_{ox}$  are the thicknesses of the semiconductor channel and oxide, respectively.<sup>8</sup> This term is central to the understanding of how the changes in the channel thickness affect the electrostatic potential in the channel. The natural scaling length represents the amount of electrostatic control the gate has over the potential in the channel. As the channel length is decreased, the natural scaling length must also be decreased to compensate for the changes in the electric field in the channel. **Equation** (1.2) can be solved by defining the potentials at the drain (x = L) and source (x = 0), such that

$$\Phi(0) = V_{bi} - \Phi_{gs} + \frac{qN_A}{\epsilon_s}\lambda^2 = \Phi_s, \qquad (1.4)$$

$$\Phi(L) = V_{ds} + V_{bi} - \Phi_{gs} + \frac{qN_A}{\epsilon_s}\lambda^2 = \Phi_d, \qquad (1.5)$$

where  $V_{bi}$  is the built-in potential at the *p*-*n* junctions between the heavily doped source/drain and the channel,  $\Phi_{gs}$  is the potential due to the applied gate voltage, and  $V_{ds}$  is the applied drain/source potential. To study the behavior under extreme SCEs, the minimum potential in the channel should be found. Making the assumptions that the

channel length is much larger than the natural length scale  $(L/\lambda \gg 1)$ , maintaining the long-channel regime, the minimum channel potential is

$$\Phi_{min} = 2\sqrt{\Phi_s \Phi_d} e^{-L/2\lambda}.$$

(1.6)

In the long-channel limit, basically a device free from SCEs, the solution is  $\Phi = 0$ . As the device size decreases, to obtain to minimize SCEs the potential minimum in the channel should be as close to zero as possible. The primary parameter for achieving this is to have a large ratio between the channel length and natural scaling length ( $L/\lambda$ ). Maintaining an effective ratio between L and  $\lambda$  determines whether the gate is still in dominant control of the channel or if SCEs dominate.<sup>9</sup> Since the minimum channel potential decays exponentially with  $L/\lambda$ , a relatively small change in this ratio has a large effect on the minimum channel potential, and  $L/\lambda \approx 5 - 10$  is usually sufficient, and any resulting SCEs are tolerable if  $L/\lambda > 2.^{8, 10, 11}$

In essence, smaller  $\lambda$  represents reduced SCEs. Based on *equation (1.3)*, there are several possible ways to decrease  $\lambda$  in a conventional FET design. Much research has been devoted to the idea of achieving higher dielectric constants of the gate dielectric material.<sup>12, 13</sup> In addition, decreasing the gate oxide thickness, is another avenue that has been pursued, but without precautions, there is a significant issue of gate leakage as the gate oxide thickness is decreased. In terms of the conventional FET design it is also possible to reduce the channel thickness, which has been explored in ultra-thin body FETs (UTB-FETs).<sup>14, 15</sup> However, UTB-FETs made from reduced channel material thicknesses suffer from increased surface roughness scattering due to bandgap nonuniformity, and any would-be performance improvement is degraded.<sup>16, 17</sup>

Conventional FET structures with Si have seemingly run their course and to continue scaling new device architectures have been realized. One such device structure that is now commercially used is the FinFET.<sup>18</sup> The FinFET has a gate wrapped around the channel and is a form of the aptly named gate-all-around FET (GAAFET). By employing this design, the natural scaling length equation is altered to give:<sup>19</sup>

$$\lambda = \sqrt{\frac{\epsilon_s}{2\epsilon_{ox}} \left(1 + \frac{\epsilon_{ox}}{4\epsilon_s} \frac{t_s}{t_{ox}}\right) t_s t_{ox}}.$$

(1.7)

In wrapping the gate around the channel, the natural scaling length is decreased by nearly 10%, indicating an increase in the amount of electrostatic control achieved and thus a reduction in SCEs. Recent production of FinFETs with an equivalent channel length of 7 nm have been realized and 5 nm nodes are expected in the coming years.<sup>4</sup> However, FinFETs are increasingly complex to fabricate and are still susceptible to SCEs. Based on this, continued miniaturization of FETs faces an imminent roadblock, while new fabrication processes and device configurations can prolong the current paradigm, ultimately, new materials must be sought.

Let us briefly quantitatively discuss the extreme limits of the scaling lengths and its relationship to channel size for a conventional FET and FinFET device structures. Suppose a thin hafnium oxide (HfO<sub>2</sub>) gate dielectric ( $\epsilon_{ox} = 25$ ) is used ( $t_{ox} = 4 \text{ nm}$ ).<sup>16</sup> The channel material in a conventional FET and FinFET structure ( $\epsilon_s = 11.9$ ), for the reasons discussed above, cannot be thinned down to atomic thicknesses without severe degradation of device performance and thus we will assume a thickness limit of  $t_s = 5 \text{ nm}.^{20}$  With these parameters, the natural scaling length for a conventional FET is  $\lambda_{\text{FET}} = 3.09 \text{ nm}$  and  $\lambda_{\text{FinFET}} = 2.81 \text{ nm}$  for a FinFET. Keeping with the requirement that  $L/\lambda \ge 2$ ,

these scaling lengths imply that the minimum channel lengths possible to avoid severe device susceptibly to SCEs for a conventional FET and FinFET are  $L_{\text{FET}} = 6.2$  nm and  $L_{\text{FinFET}} = 5.6$  nm. Notably, achieving these extreme regimes would require significant advances in the current semiconductor processing techniques, adding increasingly complex fabrication steps, but at least provide a superficial picture for the ultimate limits achievable in the future with traditional semiconductor materials.

Ultimately, the limiting factor in scaling in traditional semiconductor materials is the channel thickness. Consider, instead, a set of materials whose thickness could be thinned to one atomic layer ( $t_s = 0.65$  nm) without suffering from the bandgap nonuniformities that degrade UTB-FETs. Using this newly identified low-dimensional set of materials with a HfO<sub>2</sub> gate oxide with a thin oxide thickness ( $t_{ox} = 4$  nm), a greatly reduced natural scaling length of  $\lambda_{low-D} = 0.64$  nm. This is a significant decrease in the scaling length compared to that possible for conventional FETs and FinFETs. Similarly, the minimum channel length achievable in such a material with this scaling length is  $L_{low-D} = 1.3$  nm. If a set of materials could be identified that could achieve this scaling range, then the ability to deal with SCEs in extreme length scales would be greatly improved. The ability to mitigate SCEs in this regime would allow for the continued growth of transistor technology for many decades to come.

### 1.2 Two-Dimensional Materials and Transition Metal Dichalcogenides

In the pursuit of identifying new materials immune to SCEs, two-dimensional (2D) materials have emerged as a promising candidate. 2D materials differ from other typical semiconductor materials (e.g. Si, GaAs, Ge) in that they are layered materials. As a result, they can be easily cleaved down to single atomic layers.<sup>21</sup> Another important structural

aspect of 2D materials is that they are free from dangling bonds and also maintain excellent bandgap uniformity which means that, unlike the UTB-FETs discussed in the previous section, they are not susceptible to increased out-of-plane scattering when decreasing the material thickness. Based on this, 2D materials have quickly gathered much attention for next-generation electronics in the post-silicon era.

The properties exhibited in 2D materials range from insulators, topological insulators, semiconductors, semimetals, metals, and superconductors.<sup>22-24</sup> With such a wide-range of material properties the list of potential applications for 2D materials is long and includes flexible nanoelectronics, spintronics, optoelectronics, and low-power digital electronics.<sup>25-</sup> <sup>30</sup> The 2D materials era was started by the isolation of graphene and the demonstration of high electrical conductivity, mechanical strength, and thermal and chemical stability in it.<sup>21, 31</sup> Initially, graphene caused much excitement due to its stunning properties, but this optmizism quickly faded as it was shown that graphene was not a semiconductor material, it lacked an instrinsic bandgap, essential for use as a channel material in digital electronics.<sup>32</sup> Efforts were made to induce a bandgap in graphene, and while this was moderately successful, the resulting performance was severely degraded, causing the loss of many of the impressive qualities sought after in devices.<sup>33, 34</sup> As a result, graphene, as a potential channel material in next-generation digital electronics was discarded. The focus then turned to other 2D materials that possess properties similar to graphene but also have a suitable intrinsic bandgap.

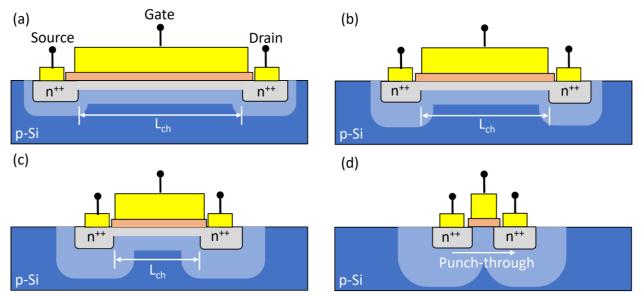

**Figure 1.3** Example of a layered TMD structure. (a) The layered structure of a TMD with MX<sub>2</sub> stoichiometry, in this case MoS<sub>2</sub>, composed of three atomic layers with Mo sandwiched between two layers of S. (b) Top view of a hexagonal lattice. Originally appeared in *Radisavljevic et al., Nature Nanotechnology*, (2011).<sup>35</sup>

Aside from graphene, another set of materials in the 2D materials family are transition metal dichalcogenides (TMDs). TMDs have a hexagonal lattice structure consisting of a layer of M atoms, a transition metal (e.g. W, Mo), sandwiched between X atoms, a chalcogen (e.g. S, Se, Te), leading to a  $MX_2$  stoichiometry as shown in *Figure 1.3*. TMD materials are layered structures with covalent bonding in the in-plane direction and relatively weak van der Waals (vdW) interactions in the out-of-plane directions which allows for relatively easy synthesis of few-layer TMDs through mechanical exfoliation. There is a significant amount of TMDs that exist in the  $MX_2$  form. *Figure 1.4* illustrates the transition metals (in purple) and chalcogens (in yellow) that can be used to form layered selenides, sulfides, or tellurides. Of the possible TMDs, group VI TMDs (e.g. MoS<sub>2</sub>, WS<sub>2</sub>, MoS<sub>2</sub>, WS<sub>2</sub>, MoT<sub>2</sub>) are the most studied and well known due to their sizeable bandgaps and stability. *Table 1.2* summarizes the group VI TMDs and their respective bandgaps. An interesting structural property of these TMDs is that in bulk form they have an indirect bandgap which transitions to a larger, direct bandgap in monolayer form due to guantum confinement.<sup>28</sup> This has led to some interesting prospects for photonic and optoelectronic applications of TMDs.<sup>29</sup>

| IIIB     | IVB | VB | VIB | VIIB |    | — VIII — | $\rightarrow$ | IB | VA | VIA | VIIA |

|----------|-----|----|-----|------|----|----------|---------------|----|----|-----|------|

| Sc       | Ti  | V  | Cr  | Mn   | Fe | Co       | Ni            | Cu | P  | S   | CI   |

| 21       | 22  | 23 | 24  | 25   | 26 | 27       | 28            | 29 | 15 | 16  | 17   |

| <b>Y</b> | Zr  | Nb | Mo  | Tc   | Ru | Rh       | Pd            | Ag | As | Se  | Br   |

| 39       | 40  | 41 | 42  | 43   | 44 | 45       | 46            | 47 | 33 | 34  | 35   |

| La       | Hf  | Ta | W   | Re   | Os | lr       | Pt            | Au | Sb | Te  |      |

| 57       | 72  | 73 | 74  | 75   | 76 | 77       | 78            | 79 | 51 | 52  | 53   |

**Figure 1.4** Transition metals and chalcogens used to form TMDs. Metals and chalcogens are highlighted in purple and red, respectively. Originally appeared in *Zhou et al., Nature,* (2018).<sup>36</sup>

| Material          | E <sub>g</sub> in bulk (eV) | E <sub>g</sub> in monolayer (eV) |

|-------------------|-----------------------------|----------------------------------|

| MoS <sub>2</sub>  | 1.2 (I) <sup>37</sup>       | 1.8 (D) <sup>38</sup>            |

| MoSe <sub>2</sub> | 1.1 (I) <sup>39</sup>       | 1.5 (D) <sup>39</sup>            |

| WS <sub>2</sub>   | 1.3 (I) <sup>40</sup>       | 2.1 (D) <sup>40</sup>            |

| WSe <sub>2</sub>  | 1.2 (I) <sup>41</sup>       | 1.7 (D) <sup>41</sup>            |

| MoTe <sub>2</sub> | 1.0 (I) <sup>42</sup>       | 1.1 (D) <sup>42</sup>            |

**Table 1.2** Bandgaps of bulk and monolayer group VI TMD semiconductors. In parenthesis the "I" or "D" indicates whether the bandgap is indirect or direct, respectively.

## **1.3 Challenges in Two-Dimensional Electronics**

Within the group VI TMDs, the two most widely studied are molybdenum disulfide (MoS<sub>2</sub>) and tungsten diselenide (WSe<sub>2</sub>). MoS<sub>2</sub> consists of molybdenum (Mo) sandwiched between sulfur (S) atoms with an indirect bulk bandgap of 1.2 eV that transitions to a direct bandgap of 1.8 eV in monolayer form. WSe<sub>2</sub> consists of tungsten (W) sandwiched between selenium (Se) atoms with a similar band structure to MoS<sub>2</sub> in bulk form that transitions to a direct bandgap of 1.7 eV in monolayer form. Despite the large amount of research on these materials, the inability to form ohmic contacts with most commonly used contact metals is a major impediment to further the understanding of these materials and their potential applications.

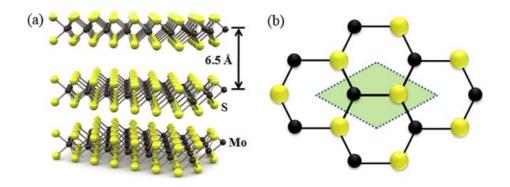

Metal-semiconductor contacts depend on several factors determined by the properties of the materials involved. When a metal with work function  $\Phi_M$  is brought into contact with a semiconductor having electron affinity  $\chi$ , charge transfer occurs between

them until the Fermi levels align at equilibrium (see *Figure 1.5 b*). In the case shown in *Figure 1.5*, when  $\Phi_M > \chi$ , the semiconductor Fermi level is initially above the Fermi level of the Fermi level of the metal before they are brought into contact with each other. To align the Fermi levels of them, the potential of the semiconductor must be raised relative to that of the metal. A depletion region forms near the junction and the positive charge due to uncompensated donors in the depletion region matching the negative charge on the metal, bending the energy bands of the semiconductor upwards. Once equilibrium is reached, a contact barrier prevents the flow of electrons from the conduction band of the semiconductor into the metal. Then, the potential barrier height  $\Phi_B$ , known as the Schottky Barrier (SB), to be overcome for injection from the metal to the semiconductor channel depends on the difference between the metal work function and the electron affinity of the semiconductor ( $\Phi_B = \Phi_M - \chi$ ). The formation of SB is inherent to all metal-semiconductor contacts and if not dealt with, severely limits current injection into the channel.

**Figure 1.5** Energy band diagram for metal-semiconductor (n-type) contacts before and after being brought into contact. (a) In this case the metal work function  $\Phi_M$  is less than the semiconductor work function  $\Phi_S$ . The values of the electron affinity  $\chi$ ,  $\Phi_M$ , and  $\Phi_S$  are measured from the vacuum level  $E_0$ , the minimum energy needed to release an electron from the material. (b) The flat band diagram of metal-semiconductor contacts under equilibrium conditions, where the difference between the metal work function  $\Phi_M$  and the electron affinity of the semiconductor  $\chi$  yields the Schottky barrier height  $\Phi_B$  of the contacts.

In theory, the SB can be reduced by choosing a metal work function with a value similar to the electron affinity of the channel material. Accordingly, the SB height then should follow the Schottky-Mott model, such that<sup>43, 44</sup>

$$\Phi_B = \Phi_M - \chi. \tag{1.8}$$

However, this is an ideal case and, in reality, metal-semiconductor contacts deviate significantly from this relation.<sup>45</sup> In reality, choosing materials whose properties follow the Schottky-Mott model has little effect on the resulting barrier height. When a semiconductor is brought into contact with a metal, the semiconductor crystal terminates at the interface. The surface of the semiconductor contains some interface states which can result from intrinsic defects in the crystal or fabrication induced defects leading to charges at the metal-semiconductor interface. Additionally, the metal-semiconductor contact is rarely abrupt. Or in other words, the metal wave function spills into the semiconductor resulting in metal-induced gap states (MIGS).<sup>46</sup> These effects combine to pin the Fermi level of the semiconductor to some position within the bandgap in a phenomenon known as Fermi level pinning (FLP). The strength of FLP can be quantified by the interface parameter pinning factor *S*

$$S = \left| \frac{d\Phi_B}{d\Phi_M} \right|. \tag{1.9}$$

If S = 1, then the Schottky-Mott model (*equation 1.8*) is followed and if S = 0, then this indicates very strong pinning.<sup>47</sup> For example, the pinning factors *S* in conventional semiconductor materials, like Si, GaAs, and Ge are known to be 0.3, 0.1, and 0.05, respectively, indicating strong pinning effects.<sup>46, 48</sup> While FLP generally adversely affects the metal-semiconductor junction resulting in larger than expected barrier heights, in conventional semiconductor devices it can be mitigated with heavily doped contact

regions. However, absent this ability in TMD materials, FLP is a major factor in forming contacts.

Several studies have been performed to determine the extent to which FLP plays a role in contacts to TMDs. For example, using a contact like scandium (Sc) whose work function is 3.5 eV should result in a significantly smaller SB height than using a higher work function metal as a contact like titanium (Ti) whose work function is 4.3 eV. However, this is not the case and there is a significant deviation from the Schottky-Mott model, resulting in pinning factor for  $MoS_2$  of S ~ 0.1.<sup>49</sup> *Figure 1.6* illustrates the FLP effect in MoS<sub>2</sub> and WSe<sub>2</sub>. Choosing metal work function values near the conduction band edge (i.e. electron affinity) of MoS<sub>2</sub> should decrease the barrier height, and likewise, choosing work function values near the valence band edge should increase the barrier height. However, as the figure shows, varying the metal work function has little effect on the tunability of the MoS<sub>2</sub> Fermi level. Therefore, the inevitable formation of a barrier in TMDs with most commonly used metals and the inability to mitigate this barrier with conventional semiconductor doping techniques is amplified by the strong FLP effects present. To appropriately assess the applicability of TMDs for applications and further investigate their intrinsic transport properties contact strategies that can overcome these challenges must developed.

Traditionally, in silicon devices the SB is dealt with by heavily doping the drain/source contact regions in a process known as ion implantation.<sup>3, 50, 51</sup> By heavily doping the contact regions, the depletion width that forms is significantly thinned so that carriers have a high probability of tunneling through the barrier. In this method, the height of the SB becomes relatively insignificant given sufficient doping concentrations. Extending this

method to TMD devices would make integration rather seamless. However, performing ion implantation doping in 2D semiconductors has proven to be impossible due to their significantly reduced thickness.<sup>52, 53</sup>

Figure 1.6 Fermi level pinning effects in (a) MoS<sub>2</sub> and (b) WSe<sub>2</sub>.

### **1.4 Contact Approaches in Two-Dimensional Electronics**

The issue of formation SB at the metal-TMD interface coupled with the strong FLP is compounded by the inability to heavily dope the drain/source regions. Conventional semiconductor doping approaches are not viable and thus new and novel approaches must be applied to make suitable contacts to TMD devices. Over the years, many approaches to making contacts have been developed. Roughly, they can be sorted into three categories: phase-engineering, chemical doping mechanisms, and interlayer contacts.

### 1.4.1 Phase Engineering

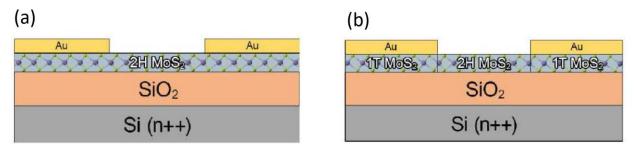

TMD layers can have several different phases. Semiconducting TMDs exist in the thermally stable 2H (trigonal prismatic) phase.<sup>54</sup> The 2H is typical in TMDs and results in the *X-M-X* (*X* = chalcogen, *M* = transition metal) stacking sequence. TMDs can also exist in a metallic 1T (octahedral) phase, which can be induced from the 2H phase.<sup>55</sup> Exploiting these phases, it is then possible to engineer ohmic contacts. *Figure 1.7* illustrates this

contact strategy, where the MoS<sub>2</sub> material underneath the contact metal is transformed from 2H-MoS<sub>2</sub> to 1T-MoS<sub>2</sub> using *n*-butyl lithium.<sup>56, 57</sup> This creates an atomically sharp phase boundary at the 1T/2H interface which results in a negligible barrier yielding drastically reduced contact resistances down to 0.2 k $\Omega$  µm.<sup>56, 57</sup> It is worth noting that this extremely low contact resistance is underestimated. The method by which this value was extracted is known as the transfer length measurement (TLM; for more see *chapter 3.5*). The TLM consists of plotting the total device resistance as a function of channel length, the contact resistance is then half the y-intercept of the linear fit. However, it is important that the total resistance of the smallest channel length is not more than a few orders of magnitude larger than the contact resistance, otherwise the total resistance will be dominated by the channel resistance rather than the contact resistance.<sup>58</sup> However, in Kappera et al. the total resistance at the smallest channel length is nearly three orders of magnitude larger than the reported contact resistance, introducing a large amount of error.<sup>56</sup> Furthermore, phase engineering is difficult to reliably control, and is not thermally stable at the necessary temperature ranges for CMOS processing.

**Figure 1.7** Phase-engineered MoS<sub>2</sub> FET. FET with Au contacts deposited on **(a)** semiconducting 2H-phase MoS<sub>2</sub> and **(b)** metallic 1T-phase MoS<sub>2</sub>. Originally appeared in *Kappera et al., APL Materials,* (2014).<sup>57</sup>

# 1.4.2 Chemical Doping

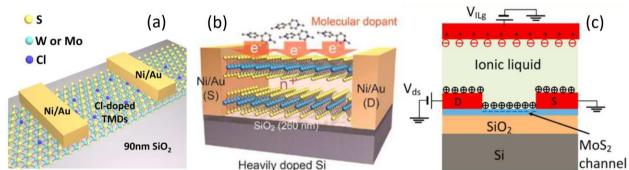

Another contact engineering method to reduce the contact barrier is to use chemical methods to achieve heavy doping profiles. Chemical dopants can effectively reduce the contact barrier at the metal-TMD interface, relying on surface charge transfer doping and the accumulation of electrons (or holes) in the channel material. These methods include doping MoS<sub>2</sub> via potassium vapor exposure, chloride molecular doping (*Figure 1.8 a*), and benzyl viologen (*Figure 1.8 b*) resulting in large drive currents, and reduced contact resistances.<sup>59-62</sup> However, these chemistry-based doping methods are difficult to control and prevent doping the entire channel material and, even still, this is not wholly effective, lacking chemical and thermal stability. Similarly, using a ionic liquid (*Figure 1.8 c*) to achieve a large double-layer capacitance to shift the Fermi level of the channel and achieve low-resistance contacts with large current on-off ratios with ambipolar transport characteristics has been achieved.<sup>63</sup> Yet this method is not practical for long-term applications as the use ionic liquid in full-scale commercial ICs is not a realistic option.

**Figure 1.8** Chemical doping methods to MoS<sub>2</sub> FETs. **(a)** Schematic diagram of CI-doped MoS<sub>2</sub> FETs using Ni/Au contacts. Originally appeared in *Yang et al., Nano Letters*, (2014).<sup>60</sup> **(b)** Diagram of MoS<sub>2</sub> FET with Ni/Au contacts using benzyl viologen doping. Originally appeared in *Kiriya et al., Journal of the American Chemical Society,* (2014).<sup>62</sup> **(c)** Illustration and working principle of a MoS<sub>2</sub> FET using an ionic liquid gate.Originally appeared in *Perera et al., ACS Nano,* (2013).<sup>63</sup>

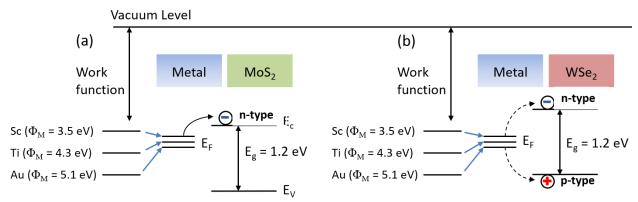

# 1.4.3 Insulating Interlayer Contacts

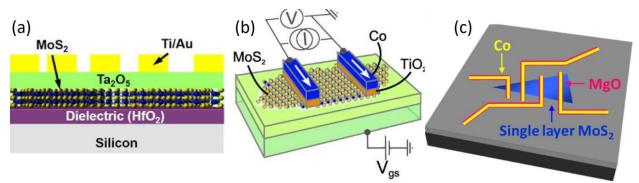

Thus far the contact engineering strategies discussed have primarily focused on trying to mimic the effects of ion implantation techniques and achieving large doping profiles at the contact interface to sufficiently thin the barrier to allow carrier to tunnel through. However, another approach is to reduce or completely remove the FLP effect all together. Essentially this relies on attenuating the MIGS by inserting some insulating interlayer material between the channel material and the contact metal, reducing the density of MIGS interaction with the channel Fermi level. To this end, ultrathin insulating materials such as metal oxides like Ta<sub>2</sub>O<sub>5</sub> (*Figure 1.9 a*), TiO<sub>2</sub> (*Figure 1.9 b*), and MgO (*Figure 1.9 c*) have been used as interlayer materials inserted between the channel and contact metal.<sup>64-66</sup> The relative band offsets, the difference between the insulating interlayer electron affinity and that of the semiconductor channel, at the Ta<sub>2</sub>O<sub>5</sub>/MoS<sub>2</sub> and TiO<sub>2</sub>/MoS<sub>2</sub> interfaces make Ta<sub>2</sub>O<sub>5</sub> and TiO<sub>2</sub> ideal for minimizing the series tunneling resistance at the contact interface. However, since semiconducting TMDs are layered and, therefore lack out-of-plane covalent bonds, depositing uniform ultrathin layers of metal oxides on them is challenging because chemical groups such as hydroxyl radical are usually required to form conformal, uniform interface layers.<sup>67-70</sup>

**Figure 1.9** Insulating interlayer contacts to MoS<sub>2</sub> FETs using metal oxides. **(a)** Schematic diagram of a MoS<sub>2</sub> FET using Ta<sub>2</sub>O<sub>5</sub> inserted between the Ti/Au contacts and the MoS<sub>2</sub> channel. Originally appeared in *Lee et al., Nano Letters,* (2015).<sup>64</sup> **(b)** Diagram of a MoS<sub>2</sub> FET using TiO<sub>2</sub> interlayer contacts between MoS<sub>2</sub> and Co contacts. Originally appeared in *Dankert et al., ACS Nano,* (2014).<sup>65</sup> **(c)** Illustration of a MoS<sub>2</sub> using MgO between the Co contacts and MoS<sub>2</sub> channel. Originally appeared in *Chen et al., Nano Letters,* (2013).<sup>66</sup>

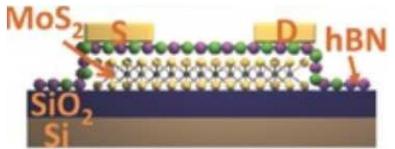

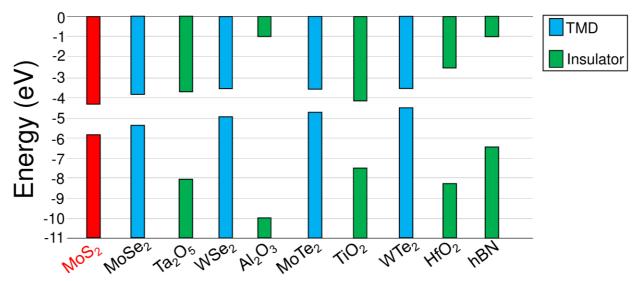

The challenge of depositing uniform and ultrathin metal oxide layers on semiconducting TMD interfaces poses a problem for continued growth of this engineering strategy using traditional oxide formation processes. On the other hand, 2D vdW materials would make better candidates as interlayer materials as they are capable of forming atomically clean and uniform interfaces without the constraints of lattice matching or surface functionalization. Ultrathin hexagonal boron nitride (hBN) has been demonstrated as an insulating interlayer contact material to MoS<sub>2</sub> (see *Figure 1.10*) to effectively reduce the SB height and the contact resistance.<sup>71</sup> However, since hBN has a relatively small electron affinity relative to MoS<sub>2</sub> there is a significant band offset between the two. This leads to a high tunneling barrier in series with the SB because the resistance of the tunneling barrier exponentially increases with the product of the barrier with and the square root of the barrier height.<sup>72</sup> Minimizing this tunneling barrier while simultaneously achieving a small SB height is key to realizing ohmic contacts with interlayers.

**Figure 1.10** hBN interlayer contacts to MoS<sub>2</sub> FET. Schematic of a MoS<sub>2</sub> FET with hBN interlayers inserted between the contact metal and the MoS<sub>2</sub> channel. Originally appeared in *Wang et al., Advanced Materials,* (2016).<sup>71</sup>

# 1.4.4 Semiconducting Interlayer Contacts

Interlayer contacts present an opportunity to achieve high-quality contacts, provided the band offset is minimized and the fabrication process can yield conformal,

intimate contact with the channel material. Some metal oxides have a favorable band alignment to MoS<sub>2</sub>, yet they cannot be deposited effectively. Conversely, hBN can be placed atop MoS<sub>2</sub> with atomic conformity and yield an ultra-clean interface, but the unfavorable band alignment between hBN and MoS<sub>2</sub> inhibits performance. Logically, if the strengths of each interlayer contact strategy could be utilized, favorable band alignment combined with an atomically thin and uniform interface, superior contacts can be formed. There are many semiconducting TMDs whose band offsets relative to each are quite small. Additionally, the formation of hetero structures by stacking semiconducting interlayers ensures atomically clean interfaces. Using semiconducting interlayers as an interlayer material to semiconducting channel materials can simultaneously minimize the tunnel barrier through favorable band alignments and high-quality interfaces through vdW bonding.

#### **1.5** Scope of the Dissertation

This dissertation focuses on the contact properties of MoS<sub>2</sub>, specifically how the addition of a 2D semiconducting interlayer affects the contacts. *Chapter 2* introduces the fabrication techniques developed and used in this research as well as the primary characterization methods. To study the impact of inserting 2D semiconductors at the contact interface, between the MoS<sub>2</sub> channel and the contact metal, MoS<sub>2</sub> FETs were fabricated with several different interlayer materials as well thicknesses. The resulting impact on the contact barrier height and how the contact resistance, resistivity, and transfer lengths change with interlayer material is presented in *chapter 3*. Ultimately, the insertion of an interlayer at the contact interface improves the contact quality substantially. *Chapter 4* discusses the details of the performance increase and how various interlayer

materials affect it. Finally, in *chapter 5* we briefly discuss the prospects for future applications of this contact method to other materials as well as its viability for use in large-scale fabrication.

# **Chapter 2 DEVICE FABRICATION AND CHARACTERIZATION**

This chapter focuses on the primary techniques and methods used to fabricate 2D FETs as well some of the methods used to characterize them. Fabricating 2D FETs requires a combination of standard semiconductor processing methods, including lithography, metal deposition, and electrical characterization, and 2D material specific techniques, such as mechanical exfoliation, vdW transfer, and nano-squeegeeing. This section gives an overview of both, with a heavier focus on the 2D material techniques.

## 2.1 Mechanical Exfoliation of 2D Materials and TMDs

Mechanical exfoliation of layered materials has been the primary way that atomically thin materials have been synthesized for device applications in a research setting. The popularity of this method started with the isolation of graphene.<sup>73</sup> Mechanical exfoliation involves continuously cleaving a bulk crystal into increasingly thinner flakes until the flakes are deemed sufficiently thin. The primary figures of merit in this process are sample size or total area, thickness, and cleanliness. The area of samples obtained is important, as many of the subsequent processing steps have relatively limited resolution (e.g. materials transfer) and material sizes on the order of tens of micrometers make these processes easier. As discussed in *chapter 1*, many 2D materials exhibit interesting properties at the atomic thickness scale and also present unique opportunities to overcome challenges related to scaling in traditional semiconductor materials. Due to this, achieving material thicknesses in few-layer and monolayer form is essential for furthering the study of 2D materials. The cleanliness of the exfoliated samples is most important, if the interface quality is not residue free then the performance of subsequently fabricated

devices will be severely affected by this. Initially, the exfoliation methods developed for 2D materials made use of "Scotch tape." The use of non-specialized tape for this task led to the introduction of large amounts of residue which ultimately hampered the device quality. In subsequent years, methods were developed to minimize the residue remaining on the surface and yield larger area flakes.<sup>74</sup> Further still, we have developed methods to exfoliate samples that are of large area, with atomic thickness, and are ultraclean, with consistency.

#### 2.1.1 Substrate Preparation and Cleaning

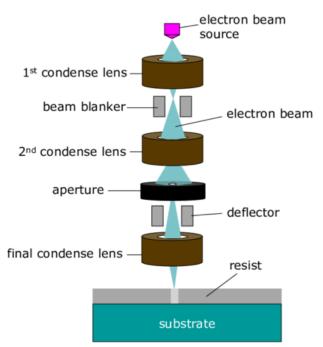

2D FETs are fabricated on substrate. In this case, a substrate of *p*-doped silicon with a silicon oxide (SiO<sub>2</sub>) layer. To assist with sample identification and subsequent processing steps, like alignment during electron beam lithography (EBL), alignment marks are needed on the substrate. These alignment marks are made on a 4-inch wafer, using a standard photolithography process, the subsequent substrate pieces are then cut from the wafer.

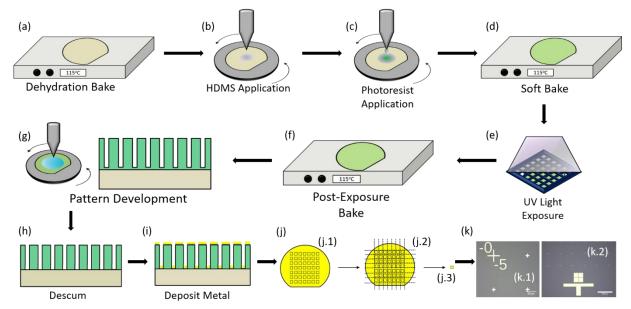

**Figure 2.1** outlines the processing steps used to make alignment marks. The wafer must be free of contaminants and moisture, both of which can cause processing problems in the later steps of lithography processing. Si/SiO<sub>2</sub> wafers have polar surfaces and thus are likely to absorb moisture. To remove moisture that may have been absorbed by the wafer, it is dehydrated on a heating element. Hexamethyldisilazane (HDMS) is an adhesion promoter that is applied to the wafer surface after dehydrating the surface. HDMS makes the surface hydrophobic, ensuring that the photoresist (PR) that is subsequently applied, adheres well to the wafer. Once the PR is spun on through a spin-

coating procedure, a soft-bake is performed. Soft baking is done for a number of reasons, it drives away the solvents contained in the PR, it further improves the adhesion of the PR to the wafer, and also anneals the stresses introduced during the spin-coating procedure. Once the wafer has been prepped through PR application and soft baking, it undergoes a UV (ultraviolet) light exposure which forms a pattern on the wafer. This is accomplished by using a mask which defines the areas on the wafer surface where the pattern defined by the mask will be transferred. When using a positive PR, the areas exposed by the UV light become more soluble. After the wafer is exposed, a postexposure bake (PEB) is performed to assist with the chemical reactions taking place in the PR due to exposure. The PEB is then followed by pattern development. To develop the pattern, the wafer is immersed in a solvent which removes the more soluble areas (i.e. the areas exposed). While the development step removes a majority of the exposed areas, a thin layer of resist still remains on the surface. To remove this thin film of PR an oxygen plasma, or descum process, is performed to remove the remaining layers. Metal (typically Ti/Au) is then deposited in the exposed area through an evaporation process, coating the entire wafer. The wafer is then cut into ~ 2 cm x 2 cm squares and submerged in acetone to liftoff the PR and metal from the surface. This results in a substrate with alignments necessary for further processing.

**Figure 2.1** Workflow diagram of photolithography process for making alignment marks. The wafer is first prepped using a **(a)** dehydration bake to remove any absorbed moisture and **(b)** HDMS is applied to act as an adhesion layer between the photoresist (PR) and the surface of the wafer. **(c)** PR is spun on and (d) soft baked to remove any solvents in the resist. Using a contact aligner, the wafer is **(e)** exposed to UV light then **(f)** baked to assist the chemical reactions in the resist. Next, the exposed pattern is **(g)** developed. This is followed by a **(h)** descum, where low-power oxygen plasma is used to etch away any remaining PR residue on the surface of the wafer. **(i)** Metal is deposited in the exposed areas. **(j)** The result is a 4-inch wafer with many different substrates of **(j.1)** ~ 2 cm x 2 cm, which is then **(j.2)** cut into smaller pieces resulting in many **(j.3)** single substrates. **(k)** Each individual substrate is then lifted off in acetone and sonicated revealing a **(k.1)** coordinate system for use during alignment in electron beam lithography and a **(k.2)** large alignment mark for orientation during this process.

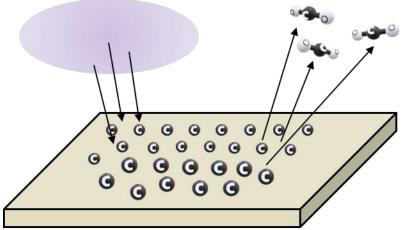

In exfoliation it is essential that the substrate surface is free of contaminants, such

as moisture and other organic materials as this ensures that the exfoliated crystals can adhere sufficiently to the surface of the substrate. To achieve this, an oxygen plasma cleaning step is performed on the substrates prior to application of the exfoliated tape. In this step the contaminants and impurities are removed from the surface. Oxygen plasma contains atoms, molecules, ions, electrons and free radicals all of which interact with the surface of the substrate as shown in **Figure 2.2**. Together, these work to remove any contaminants and organic materials, leaving an ultraclean substrate surface.

Figure 2.2 Oxygen plasma cleaning of SiO<sub>2</sub> substrate.

### 2.1.2 Mechanical Exfoliation

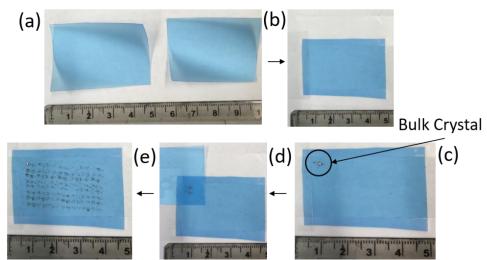

Once the substrates have been fabricated and properly cleaned through oxygen plasma, the tape used for mechanical exfoliation of ultrathin 2D flakes is prepared. A special residue reducing tape is used to minimize the transfer of contaminants, ensuring that the cleanliness of the resulting flakes will be better than those made from "Scotch tape." The tape is cut into two equal parts as shown in **Figure 2.3(a)** and the protective backing removed from each (**Figure 2.3 b**). The bulk crystal of the material to be exfoliated is placed in the top corner of one of the pieces of tape (**Figure 2.3 c**) and the second piece of tape is placed over top the crystal and pressed (**Figure 2.3 d**). This process is repeated until each of the pieces of tape are covered with thin flakes as shown in **Figure 2.3(e)**. By repeatedly cleaving the bulk crystal from each the tape the samples are continuously thinned before they are transferred to the substrate surface. To maximize the chances of creating ultrathin samples with large area, the density of

exfoliated flakes is important. The larger the density of exfoliated crystals, the higher the probability that these ideal flakes will be transferred to the substrate.

**Figure 2.3** Exfoliation using ultraclean tape. (a) Tape is cut into two squares. (b) The backing is peeled back and (c) the bulk crystal is placed in the top corner. (d) The second piece of tape is placed over top of the crystal and (e) peeled back repeatedly thinning the crystal.

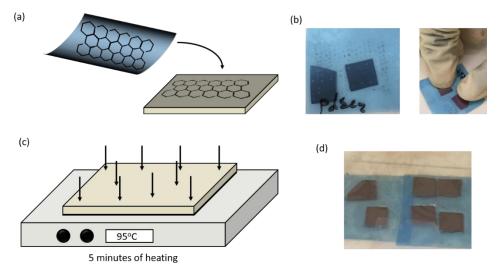

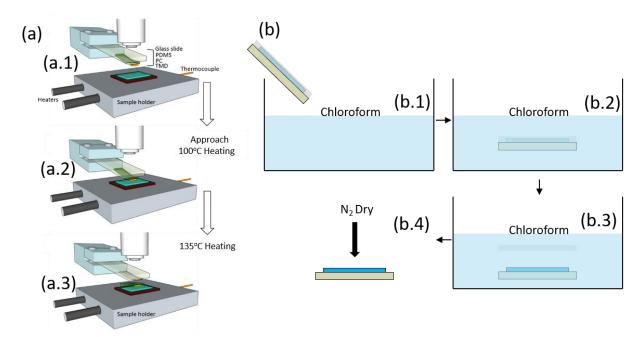

Now that the crystal has been exfoliated on tape and the substrate has been cleaned through a oxygen plasma process, the tape is placed on the substrate (**Figure 2.4** *a*). The tape is then pressed continuously for approximately five minutes (**Figure 2.4** *b*). Pressing the tape functions to remove any air that is trapped between the substrate and tape, promoting adhesion between the 2D flakes and substrate. Traditionally, the next step in the exfoliation process would be to remove the tape from the substrate. However, this usually leads in a low yield of high-quality flakes. To facilitate more consistent realization of high-quality flakes a heating step has been introduced before tape removal.<sup>74</sup> In this heating step the substrate was placed facing up (i.e. tape away from the heating element). This method, while offering some improvements from those previously performed, does not reach the full potential of heating. Instead, we have developed, and introduced some innovations to this method which greatly increase the

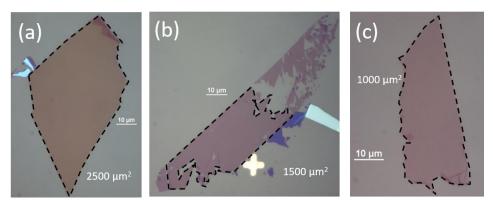

yield. After pressing, the tape/substrate is placed face down on the heating element (i.e. tape towards the heating element) as shown in Figure 2.4(c, d). This modification serves to remove any remaining air pockets between the tape and substrate by allowing the tape and its backing conform around the substrate, squeezing it tightly, creating a seal. This guarantees maximum intimate contact between the crystals on the tape and the substrate. In addition, previous methodologies posited that it was best to remove the tape from the heat and peel it in a slow, steady motion. However, this still leaves some residue on the surface and does not provide maximal yield. To avoid such issues, we do not allow the substrate/tape to cool before removing the tape. Instead, while still in contact with the heating element, the tape is removed from the substrate. Since the tape is still warm and partially melted, the adhesion glue on tape is melted enough so that it no longer adheres strongly to the substrate, while the flakes on the tape now adhere more strongly to the substrate through vdW bonding leaving residue free surfaces. Figure 2.5(a-c) show examples of exfoliated 2D flakes resulting from this innovative exfoliation method. Clearly, it yields large-area samples that are atomically thin with a residue-free surface.

**Figure 2.4** Heating exfoliation of 2D materials. (a) The exfoliated tape is placed on a clean SiO<sub>2</sub> substrate and (b) pressed continuously to remove and air traps. (c) The

tape/substrate is placed crystal side down on the heating element for 5 minutes at  $95^{\circ}$ C, (d) creating a seal around the substrate and the tape is removed from the substrate while still in contact with the heating element.

Figure 2.5 Examples of large-area exfoliated (a) WSe<sub>2</sub>, (b) MoS<sub>2</sub>, and (c) MoSe<sub>2</sub> flakes on SiO<sub>2</sub> substrates.

### 2.2 van der Waals Assembly of 2D Materials and TMDs

In fabricating devices with 2D materials and TMDs, an important process is the ability to reliably pickup and transfer exfoliated materials. Using this method, exfoliated materials can be aligned, stacked, and transferred onto one another with a high degree of precision and cleanliness.<sup>22, 75, 76</sup> To accomplish this, we have used and improved upon a dry pickup method. This method removes some of the issues related to other materials transfer and growth methods, like CVD or other PMMA based methods which can introduce some residue.<sup>75, 77</sup>

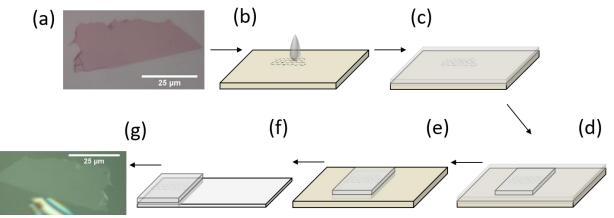

#### 2.2.1 Dry Pickup Method

The dry pickup method is facilitated by first placing a thin film of polycarbonate (PC) on a glass microscope slide using a polydimethylsiloxane (PDMS) stamp as a backing. The PC film is prepared by, first combining 3.0 g of PC with 0.18 mL of chloroform (~16:1 ratio) and placing it on a shaker for approximately 30 minutes to allow

the PC and chloroform to combine. After this time the PC will be fully mixed with chloroform, creating a viscous solution that can be spread on the PDMS stamp that has been cut into small square (~  $0.5 \times 0.5 \text{ cm}$ ). The PC is placed on the PDMS stamp using a micropipette so that a small amount (~  $20 \mu$ L) is spread on the stamp and flattened. The PC is then allowed to dry on the PDMS stamp for 5 minutes.

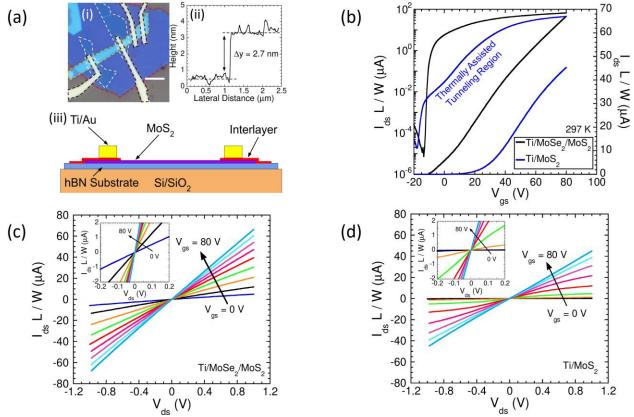

**Figure 2.6** Steps involved in picking up a 2D flake from SiO<sub>2</sub> substrate. (a) The sample desired for pickup is (b) covered with PC film and (c) flattened over the sample. (d) A PDMS is cut and placed over the PC film and sample. (e) The excess PC film and PDMS is cut away and the PDMS/PC/sample is (f) picked up from the substrate and (g) put on a glass slide.