Wayne State University Dissertations

1-1-2017

# Quantum Capacitance Study Of Novel Two- And One-Dimensional Systems

Zhe Wu Wayne State University,

Follow this and additional works at: https://digitalcommons.wayne.edu/oa\_dissertations

Part of the Physics Commons

# **Recommended Citation**

Wu, Zhe, "Quantum Capacitance Study Of Novel Two- And One-Dimensional Systems" (2017). Wayne State University Dissertations.

https://digitalcommons.wayne.edu/oa\_dissertations/1756

This Open Access Dissertation is brought to you for free and open access by DigitalCommons@WayneState. It has been accepted for inclusion in Wayne State University Dissertations by an authorized administrator of DigitalCommons@WayneState.

# QUANTUM CAPACITANCE STUDY OF NOVEL TWO- AND ONE-DIMENSIONAL SYSTEMS

by

# ZHE WU

# DISSERTATION

Submitted to the Graduate School

of Wayne State University,

Detroit, Michigan

in partial fulfillment of the requirements

for the degree of

# DOCTOR OF PHILOSOPHY

2017

MAJOR: Physics

| Approved By: |  |  |

|--------------|--|--|

|              |  |  |

|              |  |  |

| Advisor      |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

|              |  |  |

© COPYRIGHT BY

$\mathbf{ZHE}\ \mathbf{WU}$

2017

All Rights Reserved

# **DEDICATION**

I dedicate my dissertation work to my family and friends.

#### ACKNOWLEDGEMENTS

I would like to thank to everyone from quantum transport group. Among them, I want to thank my advisor, Dr. Jian Huang most. Under his guidance, I would be possible to finish my PhD in last five years and write his dissertation. Thanks to other lab mates, Talbot, Vinicio, Parisa. Thanks to Dr. Zhixian Zhou for helping with fabricating devices and suggestion on academia as well as career. Also thanks to my friend Hsun-Jen Chuang and other friends from Dr. Zhou's lab helping with transfer layer structure material. Thanks to Dr. Boris Nadgorny's suggestion in my prospectus and his class in thermal dynamics as well as condensed matter physics. Thanks to Dr. Ratna Naik's encouraging in my PhD. I also want thanks to Dr. Jogindra Wadehra's help with graduate fairs and his electrodynamics class. Thanks to Dr. Ivan Avrutsky for his suggestion on my PhD prospectus. Thanks to Ehab with helping us to use PPMS and discussion. The front desk staffs Deloris Cowen and other people are very nice and helpful. Thanks to my Chinese friend Jinjin Pan, Xinxin Woodward, Xinqiang Cai, Wenquan Zhou, Yu Gao and Shanshan Cao from physics department.

I want to acknowledge NSF funding DMR-1410302 for support.

# TABLE OF CONTENTS

| Dedication                                      | ii  |

|-------------------------------------------------|-----|

| Acknowledgments                                 | iii |

| Chapter 1 Introduction                          | 1   |

| Back ground & Motivation                        | 1   |

| Theory                                          | 4   |

| $VO_2$ introduction                             | 10  |

| GaAs introduction                               | 14  |

| Chapter 2 Fabrication                           | 17  |

| Basic of fabrication                            | 17  |

| Fabrication on GaAs device                      | 18  |

| Fabrication on $VO_2$ device                    | 29  |

| Chapter 3 Measurement techniques                | 35  |

| Transport measurement                           | 35  |

| Low temperature                                 | 40  |

| Quantum Capacitance measurement                 | 46  |

| Gating and dielectric                           | 52  |

| Chapter 4 Study on Polycrystalline $VO_2$       | 55  |

| Polycrystalline VO <sub>2</sub> characteristics | 56  |

| Challenges                                      | 56  |

| Measurement Method                              | 58  |

| Results                                         | 60  |

| Chapter 5 Study on Single crystal $VO_2$ nanobeam | 66  |

|---------------------------------------------------|-----|

| Background                                        | 66  |

| Single Crystal VO <sub>2</sub> Characteristics    | 67  |

| Strain effect                                     | 71  |

| Light effect                                      | 72  |

| Capacitance on $VO_2$ single crystal nanobeam     | 73  |

| Chapter 6 Study on GaAs HIGFET                    | 78  |

| Challenging                                       | 78  |

| Results                                           | 80  |

| Chapter 7 Other measurement results               | 85  |

| p-GaAs                                            | 85  |

| Graphene result                                   | 89  |

| Chapter 8 Summary and future plan                 | 92  |

| Summary                                           | 92  |

| Future plan                                       | 92  |

| Bibliography                                      | 94  |

| Abstract                                          | 100 |

| Autobiographical Statement                        | 102 |

# LIST OF FIGURES

| Figure 1.1 Diagra            | m for Hubbard model                                                                                                               | 7  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----|

| ~                            | son localization picture: Constructive interference of back scat-                                                                 | 8  |

| Figure 1.3 Two d             | imensional Wigner crystal[1]                                                                                                      | Ĝ  |

| Figure 1.4 VO <sub>2</sub> b | and diagram                                                                                                                       | 12 |

| •                            | rystal structure: Left: Monoclinic insulating phase; right: Rutile ase                                                            | 13 |

|                              | um well formation: two bulk material in contact. Equilibrium of bend the conduction band                                          | 15 |

| - /                          | AsAlGaAs interface TEM pictures. b)Mobility improvement of                                                                        | 16 |

|                              | dow mask for sample thin film deposition. b) Shadow mask for acts deposition. c) Finished sample with contacts on it              | 18 |

| Figure 2.2 Clean             | room environment                                                                                                                  | 19 |

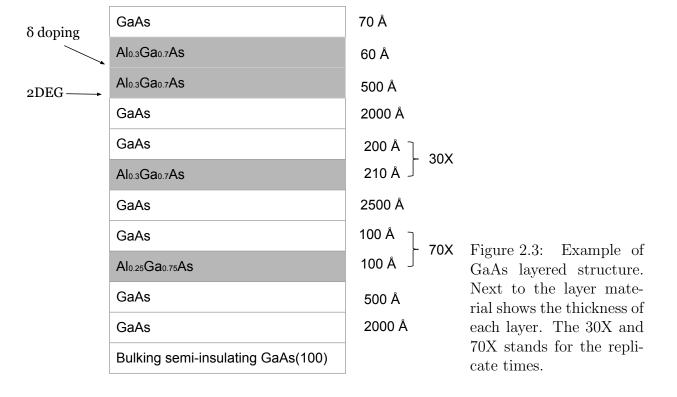

| -                            | ole of GaAs layered structure. Next to the layer material shows ss of each layer. The 30X and 70X stands for the replicate times. | 19 |

| Figure 2.4 Spin co           | oat substrate with photo resistor                                                                                                 | 21 |

| Figure 2.5 Karl S            | uss MJB3 MASK ALIGNER                                                                                                             | 22 |

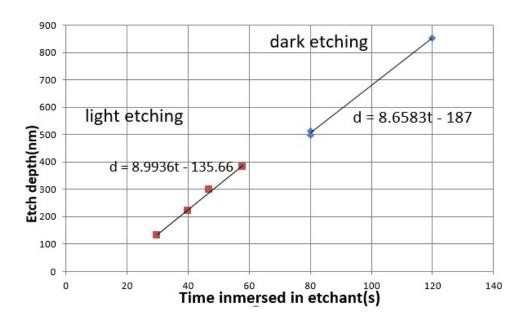

| _                            | ng rate at different conditions (Room temperature at $69.2^{\circ}F$ , t $47\%$ )                                                 | 23 |

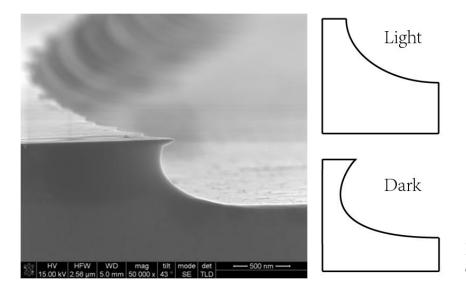

| Figure 2.7 Etchin            | g profile observed by using SEM                                                                                                   | 24 |

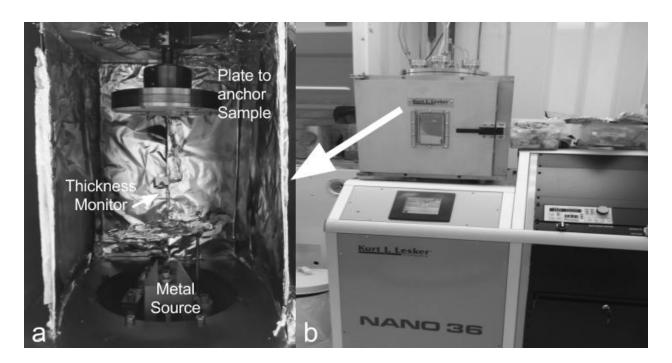

| Figure 2.8 Kurt I            | Lesker Nano36 deposition system platform                                                                                          | 25 |

|                              | rcut walls(right) vs no undercut wall(left), The black color is the blue color is photoresistor                                   | 26 |

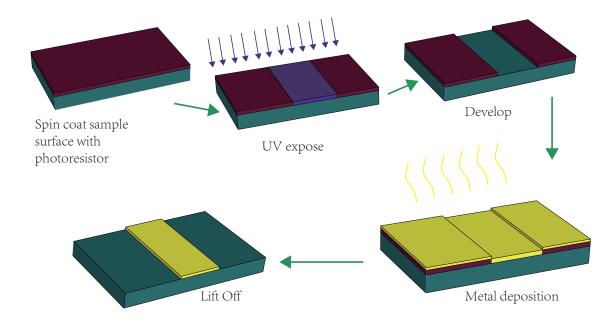

| Figure 2.10 Major            | photo lighography procedures                                                                                                      | 26 |

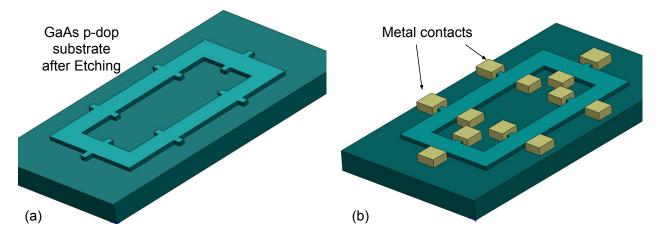

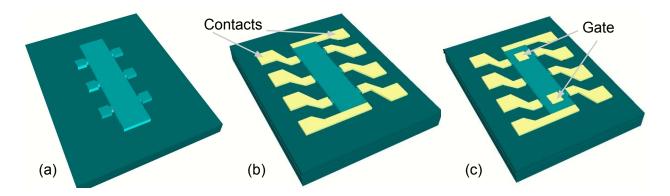

| Figure 2.11 Anti-H           | Tall bar sample fabrication                                                                                                       | 27 |

| Figure 2.12 GaAs             | HIGFET sample fabrication                                                                                                         | 28 |

| Figure 2.13 Gated p-GaAs sample fabrication                                                                                                                                                                | 29 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

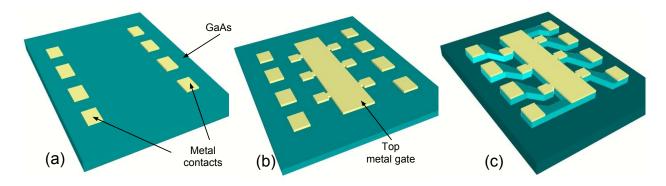

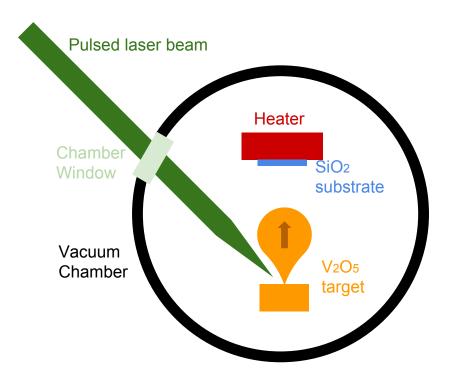

| Figure 2.14 Schematic of Pulsed laser deposition of Polycrystalline $VO_2$                                                                                                                                 | 31 |

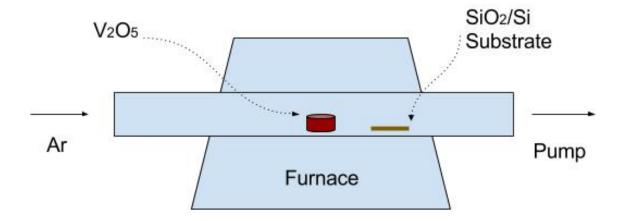

| Figure 2.15 $VO_2$ single crystal nanobeam synthesis diagram                                                                                                                                               | 32 |

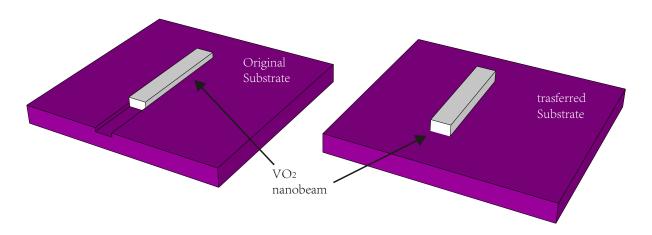

| Figure 2.16 Embedded $VO_2$ nanobeam vs Strain free $VO_2$ nanobeam                                                                                                                                        | 33 |

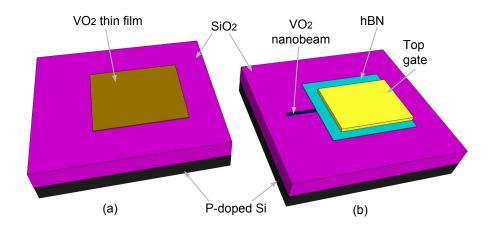

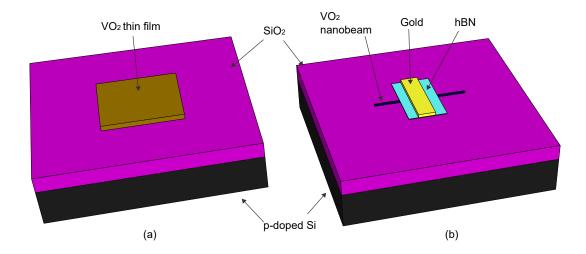

| Figure 2.17 VO <sub>2</sub> capacitance sample: a) Thin film VO <sub>2</sub> on Si substrate, the p-doped substrate serves as bottom gate. b) Single crystal VO <sub>2</sub> with top gate and bottom gate | 33 |

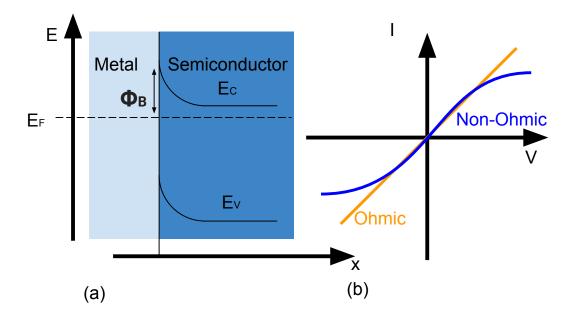

| Figure 3.1 (a) Schottky barrier forms between metal insulator junction with a height of $\Phi_B$ . (b) Ohmic contact I-V curve(orange) vs non-Ohmic contact I-V curve(blue)                                | 35 |

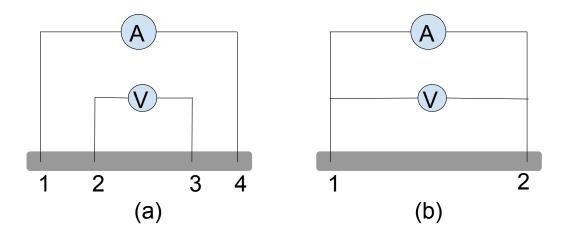

| Figure 3.2 Four terminal measurement setup                                                                                                                                                                 | 37 |

| Figure 3.3 Lock-in amplifier                                                                                                                                                                               | 38 |

| Figure 3.4 Left:Landau levels and fermi energy in a quantum hall system. Right, the longitudinal resistivity and Hall resistivity as function of magnetic field in integer quantum hall effect             | 38 |

| Figure 3.5 Quantum Hall measurement schematic                                                                                                                                                              | 40 |

| Figure 3.6 Fractional Quantum Hall effect.[3]                                                                                                                                                              | 41 |

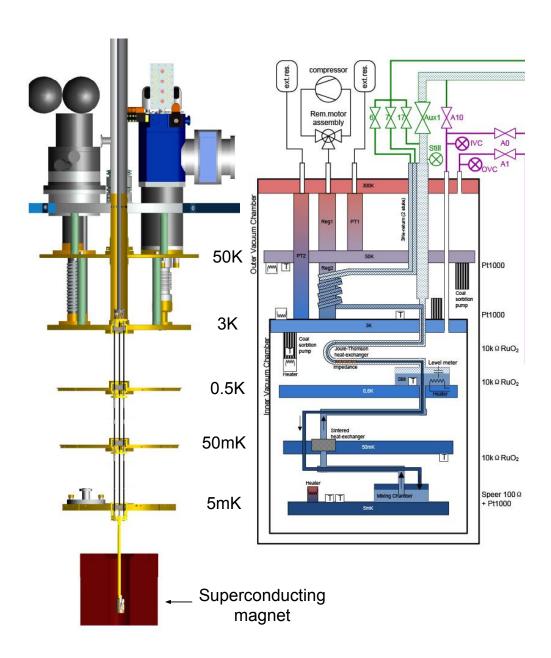

| Figure 3.7 Structure of inset of dilution refrigerator with different cooling stage .                                                                                                                      | 42 |

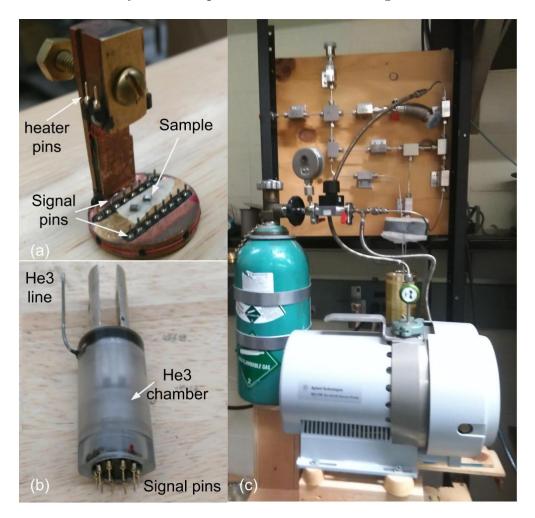

| Figure 3.8 a) Currently used sample holder. b) Helium-3 cell sample holder for better cooling purpose. c) Helium-3 cell fillempty control system                                                           | 43 |

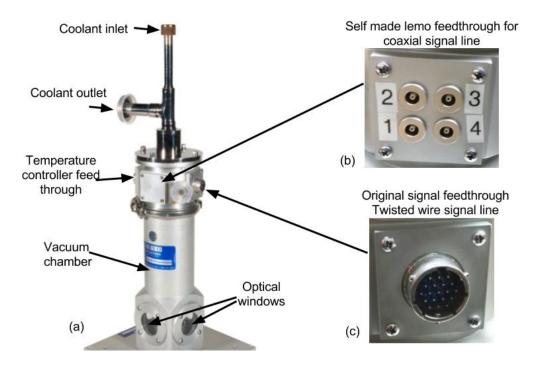

| Figure 3.9 Flow cryostat                                                                                                                                                                                   | 45 |

| Figure 3.10 PPMS system                                                                                                                                                                                    | 46 |

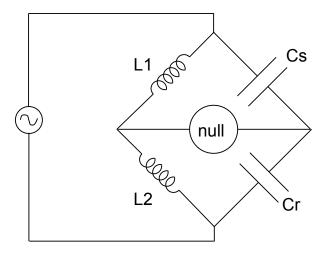

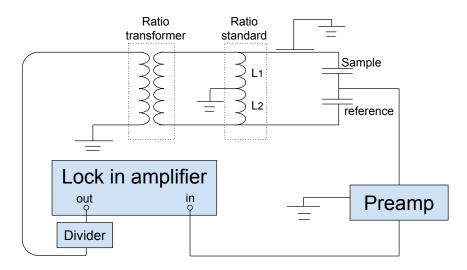

| Figure 3.11 Schematic for capacitance bridge.                                                                                                                                                              | 49 |

| Figure 3.12 Ratio transformer bridge measurement circuit                                                                                                                                                   | 49 |

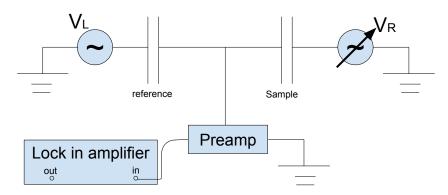

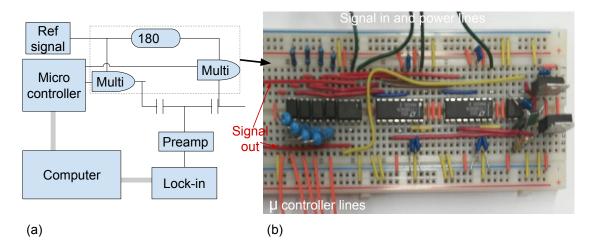

| Figure 3.13 Active bridge circuit schematic                                                                                                                                                                | 51 |

| Figure 3.14 Circuit for active bridge. (a) Circuit diagram. (b) The picture of real component of the dotted circled area in (a)                                                                            | 53 |

| Figure 3.15 $VO_2$ gating scenario: (a) gating thin film,(b) gating nanobeam                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

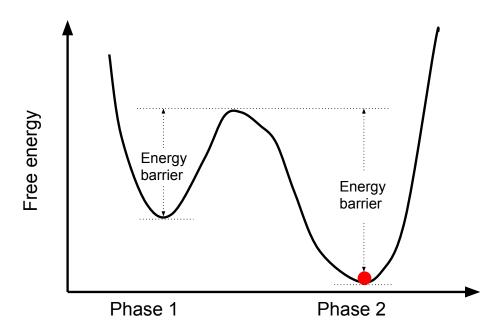

| Figure 4.1 Schematic diagram of the free energy as a function of phase parameter.[4]                                                                                                                                                                                                                                                                                                                                                                                                                          | 55 |

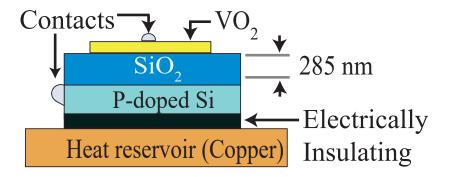

| Figure 4.2 Diagram of the polycrystalline $VO_2$ capacitance device[4]                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56 |

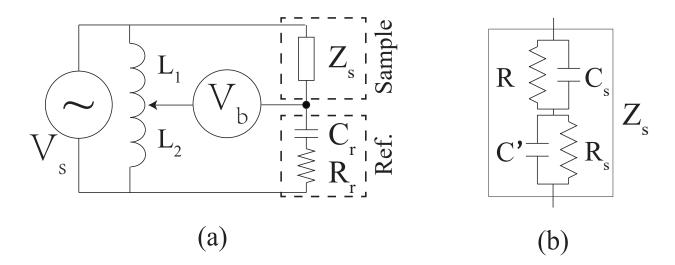

| Figure 4.3 (a) Bridge setup (b) Impedance component in the circuit.[4]                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57 |

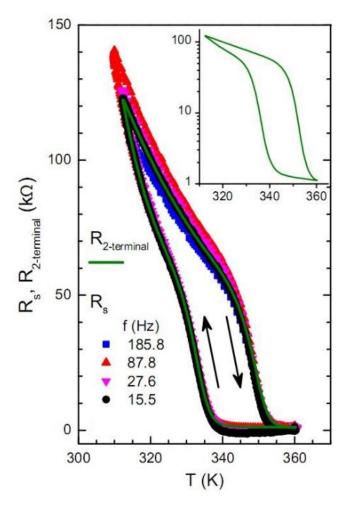

| Figure 4.4 Comparison of standard in-plane 2-terminal technique (green line) with bridge technique (scatter plots) for measuring sheet resistance. Arrows distinguish between heating and cooling cycles. The in-plane measurement is shown on a semi-log plot in the inset.[4]                                                                                                                                                                                                                               | 61 |

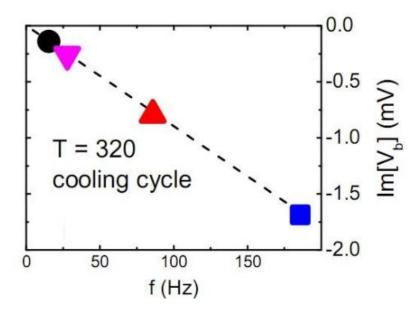

| Figure 4.5 Confirms linear relationship $\operatorname{Im}[V_b] \propto f$ from Eqn. 4.1.[4]                                                                                                                                                                                                                                                                                                                                                                                                                  | 62 |

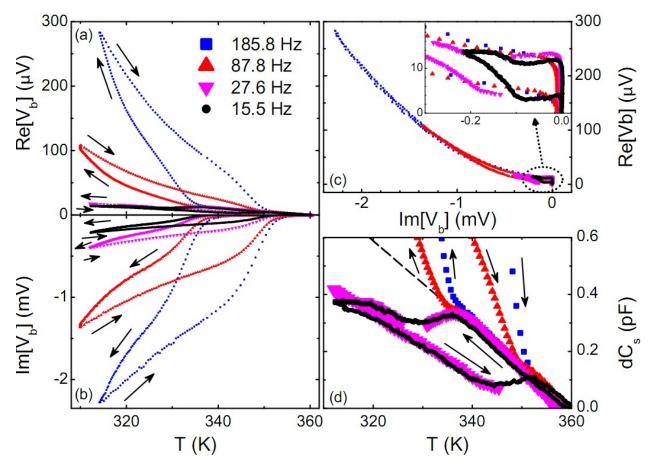

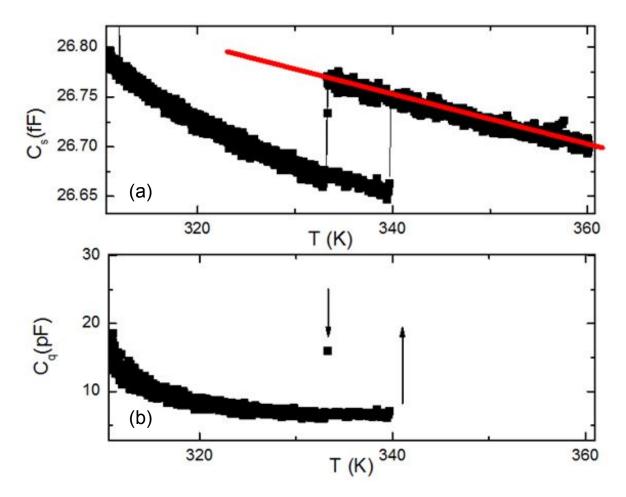

| Figure 4.6 (a),(b) $Re[V_b]$ and $Im[V_b]$ as functions of $T$ . Note the change in scale from $\mu V$ to $mV$ . (c) $Re[V_b]$ as a function of $Im[V_b]$ is a monotonic nearly single-valued function for high frequencies. Inset highlights low frequency measurement where mixing is eliminated. (d) Capacitance changes $dC_s$ as a function of $T$ . The slope of all traces in the metallic regime gives the $T$ dependence of $C_{geo}$ which has been extrapolated below the MIT as a dashed line.[4] | 63 |

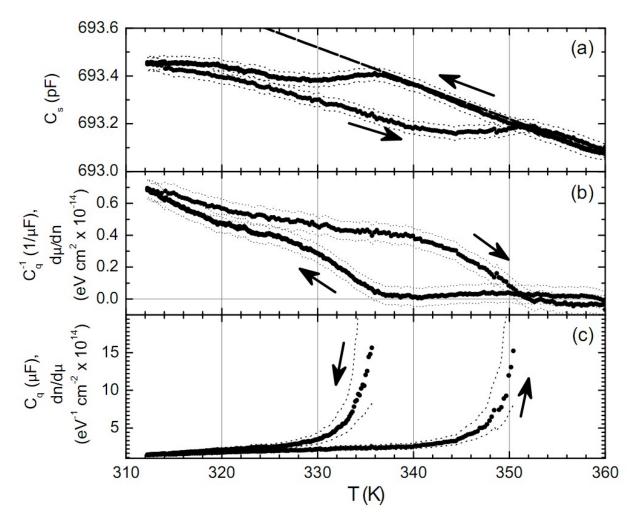

| Figure 4.7 (a), (b), and (c) $C_s$ , $C_q^{-1}$ and $C_q$ as functions of $T$ . In (c), only a portion of the thermal cycle is shown, since larger $C_q$ cannot be resolved. [4]                                                                                                                                                                                                                                                                                                                              | 64 |

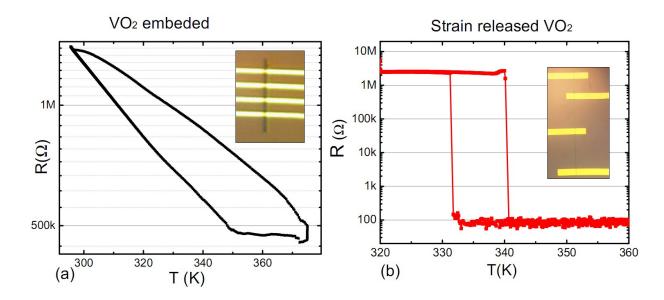

| Figure 5.1 Left:Resistivity measurement on strained $VO_2$ on substrate; Right: Resistivity measurement on strain free $VO_2$                                                                                                                                                                                                                                                                                                                                                                                 | 67 |

| Figure 5.2 Growth direction of Single Crystal $VO_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69 |

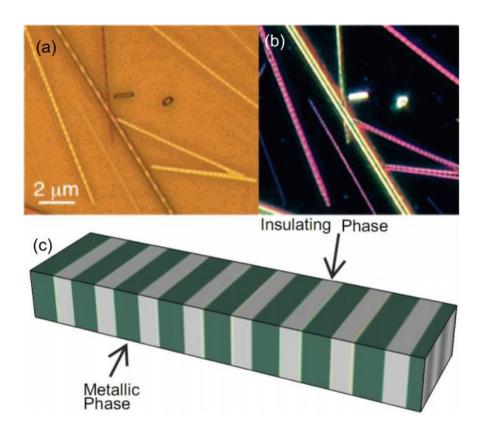

| Figure 5.3 a), b)Optical image of single crystal VO <sub>2</sub> near transition temperature shows different color alternating strips.[5] c) Schematics of insulating metallic alternating stripes                                                                                                                                                                                                                                                                                                            | 70 |

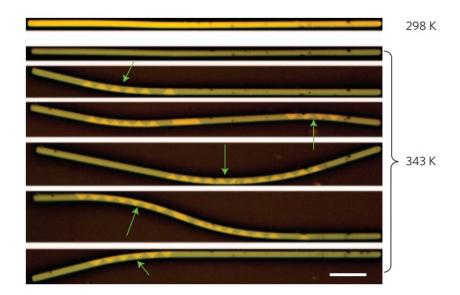

| Figure 5.4 The green arrow indicating the direction of external force applied by tungsten needle. The orange color is the insulating domain.[6]                                                                                                                                                                                                                                                                                                                                                               | 71 |

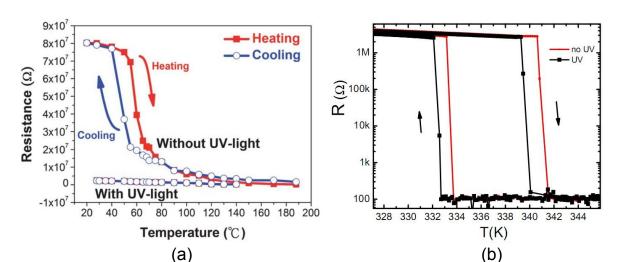

| Figure 5.5 UV light effects on VO <sub>2</sub> transition. Left figure shows the strained VO <sub>2</sub> single crystal nanobeam have transition with and without UV light[7]. Right figure shows the similar condition as left when the strain is released                                                                                                                                                                                                                                                  | 73 |

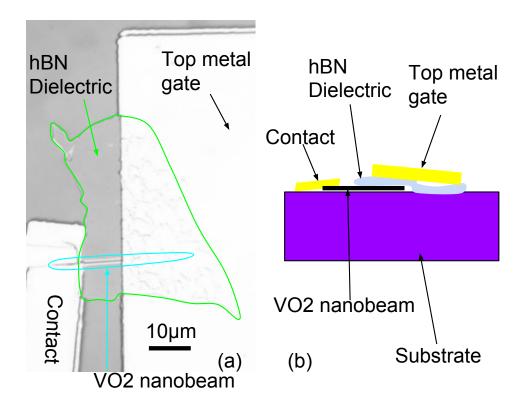

| Figure 5.6 (a) Optical image of single crystal $VO_2$ capacitor device. The dielectric is multi-layer hBN, the $VO_2$ nanobeam and top gate form an capacitor. The thickness of hBN is around 30nm. The length of $VO_2$ nanobeam underneath hBN is about $20\mu m$ . (b) Schematic of side view of the same device | 75 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.7 (a) Sample capacitance(black line) and fitted geometric capacitance(red line) as a function of temperature.(b) Quantum capacitance $C_q$                                                                                                                                                                 | 76 |

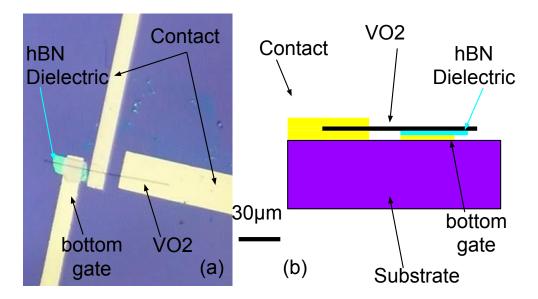

| Figure 5.8 (a) Optical image of single crystal VO <sub>2</sub> capacitor bottom gate device. This is an unfinished device, another layer of deposition need to be done on the contacts area. (b) Schematic of side view of the same device                                                                          | 77 |

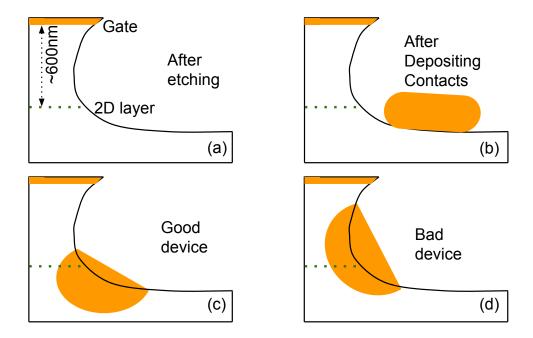

| Figure 6.1 (a) The profile after etching, (b) Metal contacts deposition, (c) After annealing, metal contacts have a good Ohmic contacts with 2D layer and have a safe distance from top gate, (d) After annealing, contacts metal are                                                                               | 79 |

| too close to top gate                                                                                                                                                                                                                                                                                               | 19 |

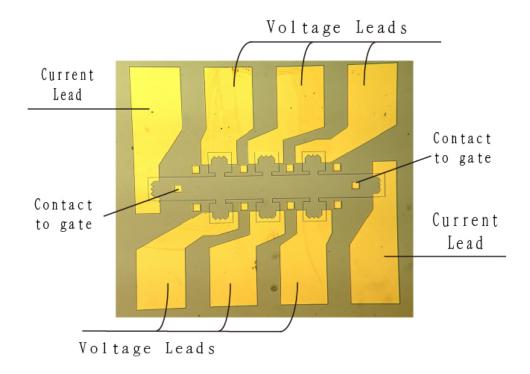

| Figure 6.2 The optical image of a working HIGFET device                                                                                                                                                                                                                                                             | 80 |

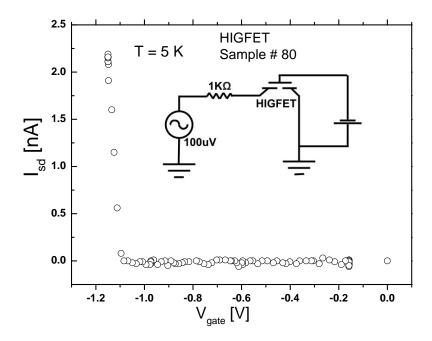

| Figure $6.3$ HIGFET turn on test. The inside is a schematic of testing circuit                                                                                                                                                                                                                                      | 81 |

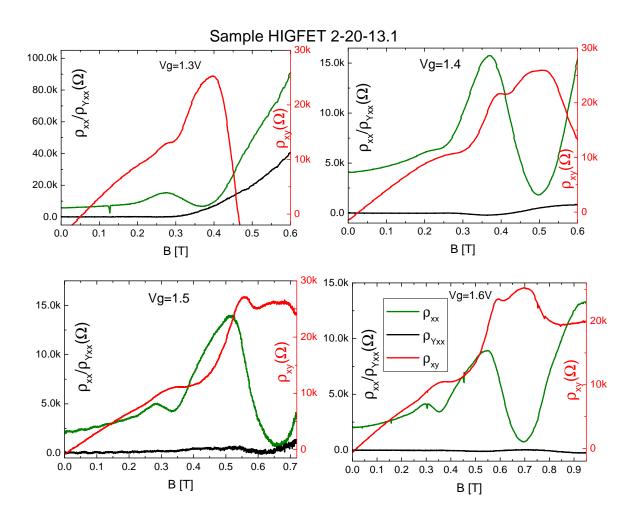

| Figure 6.4 Quantum hall measurement on HIGFET                                                                                                                                                                                                                                                                       | 83 |

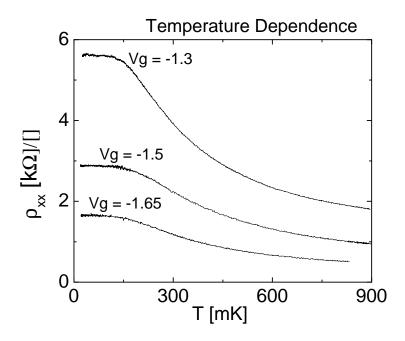

| Figure 6.5 Temperature dependence on HIGFET                                                                                                                                                                                                                                                                         | 84 |

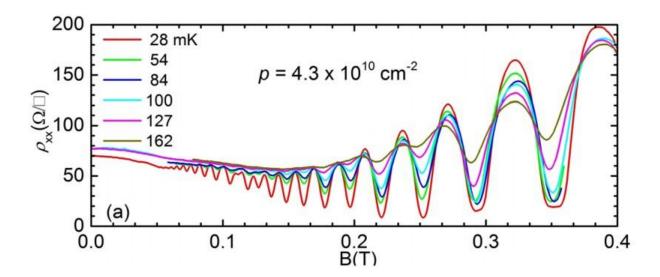

| Figure 7.1 Shubnikov-de Haas (SdH) oscillations of p-doped GaAs sample[8]                                                                                                                                                                                                                                           | 85 |

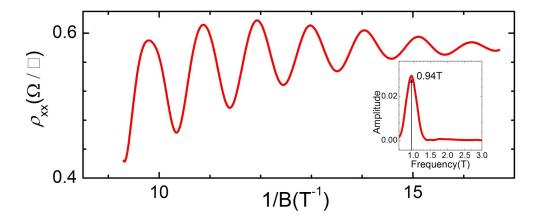

| Figure 7.2 SdH vs 1/B                                                                                                                                                                                                                                                                                               | 86 |

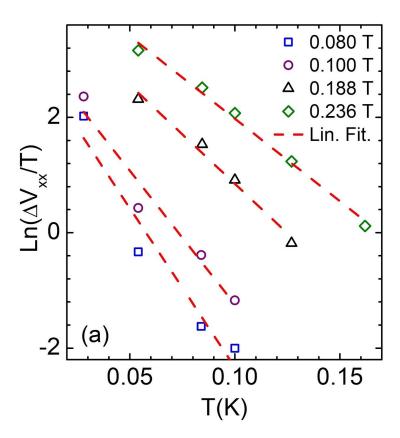

| Figure 7.3 Dingle factor                                                                                                                                                                                                                                                                                            | 88 |

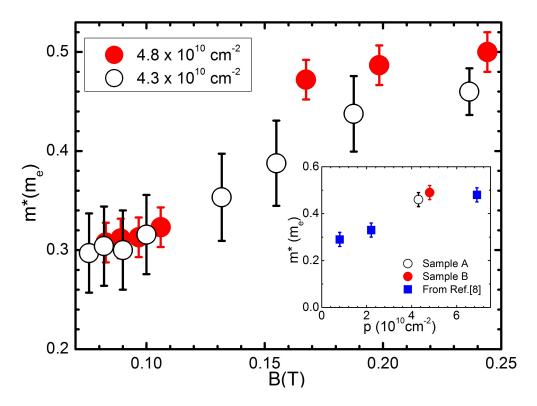

| Figure 7.4 Effective mass fitted at different magnetic field strength[8], sample B is a similar sample with density $p=4.9\times10^{10} cm^{-2}$ , Inset shows our result compared to previous data obtained through cyclotron resonance measurements [9]                                                           | 89 |

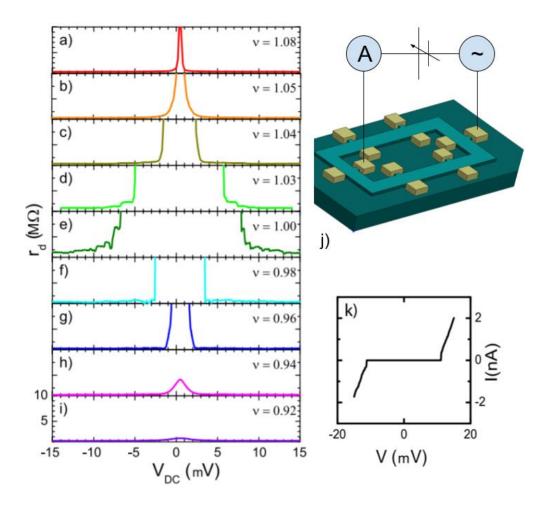

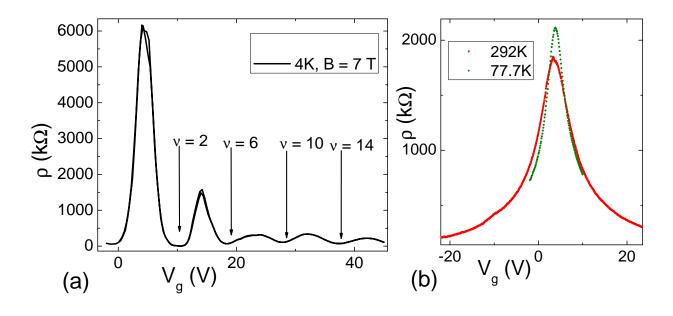

| Figure 7.5 (a)-(i) Differential resistance with variours filling factors, (j) Experimental setup for measuring the bulk conduction properties with separated edges (k) I-V curve from DC measurement at $\nu=1$                                                                                                     | 90 |

| Figure 7.6 a) Quantum hall measurement on $\rho_{rr}$ . b) Dirac point at 77.7K and 292K.                                                                                                                                                                                                                           | 91 |

#### CHAPTER 1 Introduction

## 1.1 Back ground & Motivation

Strongly correlated systems is a fascinating topic in condensed matter physics. Among them, vanadium dioxide(VO<sub>2</sub>) is a strongly correlated material which shows metal-insulator transition(MIT) near room temperature(340K)[10]. Early studies have revealed its first order transition nature [10, 11]. Electric transport behaviors as well as optical properties undergoes a tremendous change in the transition[12–14]. These makes VO<sub>2</sub> attractive as a potential functional material in optical switch and semiconductor applications [15, 16]. On the other hand, the transition mechanism of VO<sub>2</sub> is a puzzle for decades. In comparison to traditional correlated Mott insulators, VO<sub>2</sub> also undergoes a huge structural phase transition (SPT) from rutile to monoclinic phases at 340K[10]. Numerous studies have shown strong evidences to support both mechanisms. Structure transition mechanism is supported by optical evidences [17–20]. As for interaction driven mechanism, tungsten doping effects[21] and extreme pressure experiment [22] successfully changes the interaction strength to tune the transition. Nowadays researchers tend to believe both mechanisms contribute to the transition [23, 24]. They occur at identical temperature which hinders researcher to distinguish them. Recent advances have been made thanks to the synthesis of single crystal VO<sub>2</sub> by Guiton's group [5]. With a cleaner and simpler system to study, Ruan's group has implanted optical color depth and TEM diffraction to observe MIT and SPT accordingly. Two transitions can be well distinguished with placing single crystal VO<sub>2</sub> on certain types of substrates [25].

Among research works have been done to study transition mechanisms, few have been done using transport measurements. Even though transport is ideal to study the electronic structure with rich physics, a thorough search of the relevant literature yielded the following:

only two related article measuring hall effect on VO<sub>2</sub>[26, 27]; limited number of studies used carrier density tuning method (field effect) on VO<sub>2</sub> also encounter extremely difficult[28, 29] and it remains an open question whether it is due to strongly correlated interaction or short screening length limits the penetration of field effect[30].

To gain a better understanding of the MIT in VO<sub>2</sub> and obtain the electronic structure during the transition, we focus on utilizing quantum capacitance measurement to study VO<sub>2</sub>. Quantum capacitance measurement was firstly proposed for probing the electronic structure[31] and have successfully revealed strong interaction in GaAs two-dimensional electron system[32]. Our work has demonstrated a unique method to extract quantum capacitance from a large resistive sample using a home made bridge. The accurately measured capacitance yields density of states(DOS) near Fermi energy which manifests a rapid growth when temperature raises up, as expected for approaching metallic state. Our work is the first experimental study to probe during MIT in VO<sub>2</sub> and is important for unraveling the long-standing mystery behind the driving mechanism for this phase change. Additionally, the bridge method for measuring the quantum capacitance in a highly resistive sample can be readily applied to other systems that exhibit a MIT, which is universal to many systems.

The electron-electron interactions are universal in many systems. Besides Mott insulator which is due to the competition between on-site Coulomb repulsion and transfer integral, 2D charge carriers in confined quantum well also demonstrate behaviors due to e-e interactions. These are fascinating phenomena, but not yet well understood [33–36]. Researchers seek to understand the role of e-e interactions in ground state. One major question is can e-e interactions be strong enough to drive 2D charge carriers into lattice structure such as Wigner crystal [37] or Wigner glass [38–40]. For such systems, the Coulomb energy  $E_C$  com-

petes with many other factors, such as the kinetic energy  $E_F$ , disorder potential, polarizing magnetic field, etc. One of the major challenges to experimental progress in this area, is the difficulty in fabricating high purity systems with dilute charges. Furthermore, making Ohmic contact to dilute charge systems represents a significant challenge. A significant portion of this work is to fabricate ultra-high purity devices using both doped p-type GaAs/AlGaAs quantum square wells and un-doped (capacitively induced holes) heterojunction gated field effect transistors (HIGFETS). These samples demonstrate excellent mobility at low charge densities [41]. These systems allow us to identify pinning behavior in the reentrant insulating phase near filling factor  $\nu = 1/3$  in the fractional quantum Hall regime and several signatures of WC without suffering from localization effects [42]. Additionally, these samples provide a unique opportunity to probe the transport between two edges of a topological insulator that are perfectly separated by a bulk insulating phase in a corbino-disk-like geometry for integer filling factors in the quantum Hall regime [43]. These studies are critical to understanding the physics of strongly correlated charges and their relation to topological phases, which is a fascinating area of intense current research [44–48].

The content structure of this thesis as follows: Chapter 1 introduces the physics of strongly interacting systems discussed in this thesis. Chapter 2 presents the fabrication method. Chapter 3 contains the cryogeneic techniques as well as measurement methods we implement. Chapter 4 introduces VO<sub>2</sub> and discusses the quantum capacitance measurement results on polycrystalline VO<sub>2</sub>. In Chapter 5 we use single crystalline VO<sub>2</sub> to study the transition. Chapter 6 and 7 represents the result we have from GaAs correlated systems and graphene.

## 1.2 Theory

## 1.2.1 Electron in solid, Non-interacting electrons

The behavior of electrons inside solid has been studied for decades. Numerous models have been created for different systems. People started with simple free electron model: For free electrons in metal, in Schrodinger equation, there is no potential energy term. The density of state for 3D can be written as:

$$g(E)dE = \frac{V}{2\pi^2\hbar^3}(2m)^{\frac{3}{2}}E^{\frac{1}{2}}dE$$

(1.1)

Similarly, we can get 2D and 1D density of state. Integrating density of state up to Fermi energy  $E_F$  yields the total number of electrons(N), which gives us a formula of Fermi energy as a function of N:

$$E_F = \frac{\hbar^2}{2m} \left( \frac{3\pi^2 N}{V} \right)^{\frac{2}{3}} \tag{1.2}$$

Considering the transport behavior, Drude applied kinetic theory of gases to electrons in metal. It can be described as:  $j = \sigma E$  and  $\sigma = \frac{ne^2\tau}{m_e} = ne\mu_e$

The above model gives a good approximation and it's been widely used. To extend this model to include ions in solid, Born-Oppenheimer approximation is made to decouple electron and ion. The ion and electron has a large mass ratio(2000~500000) which makes ion relatively static to electron. Another approximation is mean field approximation, which lets one electron treat the interaction from other electrons through an average field. With these approximations, band theory takes the ion potential into account.

The effect of periodic lattice potential on dynamics of the conduction electron wave-

packets can be taken into account by using effective mass  $m_e$  to substitute the real mass of electron in the equation of motion. The equation of motion for electrons:

$$\hbar \frac{\mathrm{dk}}{\mathrm{dt}} = -eE \tag{1.3}$$

and group velocity can be written as  $v = \frac{d\omega}{dk} = \frac{1}{\hbar} \frac{dE}{dk}$ , Combining these together it gives:

$$\frac{\mathrm{dv}}{\mathrm{dt}} = \frac{1}{\hbar} \frac{d}{\mathrm{dt}} \left( \frac{\mathrm{dE}}{\mathrm{dk}} \right) = \frac{1}{\hbar} \frac{d^2 E}{\mathrm{dk}^2} \frac{\mathrm{dk}}{\mathrm{dt}} = -\frac{1}{\hbar^2} \frac{d^2 E}{\mathrm{dk}^2} eE$$

(1.4)

Also using  $m_e \frac{dv}{dt} = -eE$ , finally we can define effective mass as:

$$m_e = \hbar^2 \left(\frac{d^2 E}{dk^2}\right)^{-1} \tag{1.5}$$

The band theory has been successfully used in many cases in solid state physics [49]. It well distinguishes insulator and conductor, and it gives guidance for engineering the properties of materials. However, people discovered in special cases [50] band theory gives the invalid result.

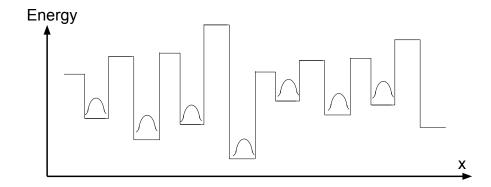

In certain system[51], when provided with large amount of random disorder, it turns out to be an insulator even there is zero band gap. Anderson studied this disorder driven insulating which is called Anderson Localization. The electron is in phase coherent with its time reversal state. This coherent interference traps electron at the disorder site. The phase coherence can be changed by applying magnet field, which breaks the time reversal symmetry.

In disorder free systems, for example single crystal VO<sub>2</sub> and ultra clean GaAs/AlGaAs

herterojunction, localization of carriers happen as well and leads to insulating behavior.

This tells us there are other effects we should take into account which is shown in following section.

# 1.2.2 Strongly correlated system

When dealing with the interaction among electrons, band theory treats electron-electron interaction in mean field approximation: one electron feel an averaged electric field which is from other electrons around. Is this always true? In most cases, when electron-electron interaction is not dominant effect, it will be overwhelmed by other effects(electrons kinetic energy). The mean field approximation works well when dealing with these cases. For some systems, when interaction between electrons becomes comparable to its kinetic energy, we have to take into account the interaction to get a complete picture.

#### 1.2.3 Hubbard model and Mott transition

Hubbard model is widely used to describe the transition from metal to insulator in Mott insulator. It illustrates interacting particles on a lattice. In modern *ab initio* calculations, the local density approximation is improved by introducing a Hubbard U term to include on-site repulsion effect[52] in transition metal.

For electrons inside solid, tight-binding model only includes the hopping term. Hubbard model has been improved by taking strong interactions into account. Although in most cases, it gives qualitative answer. It successfully predicted Mott insulators which is insulating due to the repulsion between in site electrons.

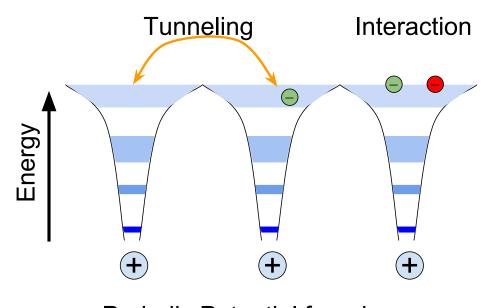

Hubbard model takes an extra term called on-site repulsion in Hamilton. Which is due to the coulomb repulsion between electrons from same atomic orbitals. As shown in Figure.

1.1, in band theory, there is only the kinetic term which decides hopping (or tunneling) be-

havior. However, by introducing on-site repulsion, Hubbard model considers the competition between hopping and on-site repulsion. Although Hubbard model only considered adjunct site hopping integral and Coulomb repulsion, it is the simplest effective model to take the interaction into account.

Periodic Potential from ions

Figure 1.1: Diagram for Hubbard model

The Hamiltonian can be written as:

$$H = H_t + H_U = -\sum_{\langle i,j \rangle \sigma} t_{ij} c_{j\sigma}^{\dagger} c_{j\sigma} + U \sum_i n_{i\uparrow} n_{i\downarrow}$$

(1.6)

The first part  $H_t$  is called transfer(hopping) integral, which stands for kinetic energy term. Second part  $H_U$  is Coulomb repulsion term called Hubbard U. The typical Mott insulator comes from transition metal oxides, amorphous semiconductors, etc[53, 54]. The system is an insulator when electron-electron Coulomb interaction is larger than its kinetic energy. Why most Mott insulators happens at transition metal oxides? To answer this question, we have to consider their sub band structure. For transition metal oxides, their 3d band and 2p band has a large gap. When there 3d band is half filled, the  $H_t$  is much smaller than those system which has a larger overlapping between out shell band and inner band. In this situation,  $H_t$  becomes comparable to  $H_U$  term. When  $H_U$  is strong enough ,it becomes a correlated insulator. This behavior can be tuned by external gating, carrier injection[10, 55, 56], ultra high pressure as well as doping.

# 1.2.4 Anderson localization

Figure 1.2: Anderson localization picture: Constructive interference of back scattering.

The phenomenon of Anderson localization happens at the ground state. The Anderson localization happens due to the large amount of random disorder. The resistivity temperature dependence of Anderson localization follows Arrhenius hopping. It is predicted as the activated behavior where  $\rho \propto \exp(T_0/T)$ . This provides us with the right way to distinguish the Anderson insulator from Wigner crystal.

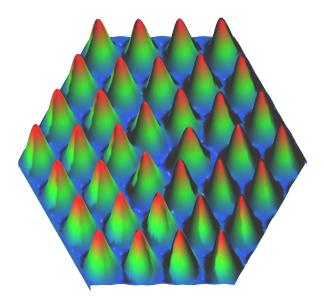

#### 1.2.5 Wigner crystallization

Wigner crystal is a solid state phase of electrons. The cause of Wigner crystallization is similar to Mott insulator. Electrons crystallize when Coulomb interaction dominates the kinetic energy. The system indicates insulating behavior. The Wigner crystallization normally

requires ultra low temperature to lower the kinetic energy. For example, the first observation of Wigner crystal is observed on Helium surface where electrons form solid[57]. Compared

Figure 1.3: Two dimensional Wigner crystal[1]

with Mott insulator which electrons localize at ion lattice site, Wigner crystallization happens when electrons form its own lattice. It happened when electrons are confined within energy potential. As for the Wigner crystal on Helium surface, a potential well formed by the combination of the image potential and repulsive barrier to penetrate into the liquid[57]. The electrons is not moving freely in the 2D surface before Wigner crystallization happens. As an intermediate step, two dimenstional electron gas goes into Fermi liquid before goes to Wigner crystal. With the prove that Wigner crystal exists, naturally the next question is whether Wigner crystal exist inside solid. To achieve Wigner crystal, we need a large  $r_s$  value. Several theoretical predictions gives minimum  $r_s$  for Wigner crystallization in different systems[58, 59]. All  $r_s$  requires to be at least the order of 10. One of the ideal systems people have been found to realize Wigner crystal is quantum well formed in GaAs/AlGaAs

heterojunction. To be able to reach the Wigner crystal, normal it needs to reach a low density to tune up the  $r_s$ . From Derude's formula:  $\sigma = ne\mu$ , when density is too low, there is a trouble to measure electrical signal since the conductivity  $\sigma$  goes down. The only way to resolve this is to achieve a high mobility to compensate the effect from low density. Since GaAs/AlGaAs has a very high mobility, therefore it is an ideal candidate for achieving this goal. Another reason is that GaAs/AlGaAs heterojunction has an almost ideal interface, this fact limits the possibility for the disorder driven Anderson localization. The Wigner crystal are predicted to have a resistivity temperature dependence behivor follows Efros Shklovskii hopping. It is a non-activated behavior where  $\rho \propto \exp(T_0/T)^{1/2}$ . This provides us the very important way to distinguish Wigner crystal from Anderson insulator.

# 1.3 VO<sub>2</sub> introduction

VO<sub>2</sub> is a strongly correlated material. It attracts attention due to its near room temperature Metal insulator transition(MIT). VO<sub>2</sub> undergoes transition from insulator to metal around 340K[10]. The resistivity during the transition changes many orders. There are only few materials has MIT transition near room temperature: VO<sub>2</sub>(340K), NbO<sub>2</sub>(1080K), Ti<sub>2</sub>O<sub>3</sub>(410K), and V<sub>2</sub>O<sub>3</sub>(150K)[10, 60]. Among them, VO<sub>2</sub> shows closest transition temperature to room temperature. It also shows first order transition which happens with abrupt properties changes on electrical conductivity, optical transmittance. These features make VO<sub>2</sub> potential for electronic applications including fast switches, sensors, memories.

The electron-electron interaction in  $VO_2$  can not be ignored when study the electrical properties. However, electron-electron interaction is not the only mechanism for transition. The structure of  $VO_2$  changes from monoclinic insulator to rutile metal. The transition happens with hysteresis. Depending on the crystal structure, the hysteresis can be progressive

| Phase      | Symmetry                | Lattice Constant(Å)              |                 |                 | Angle          |

|------------|-------------------------|----------------------------------|-----------------|-----------------|----------------|

| Rutile     | $P4_2/mnm(D_{4h}^{14})$ | $a_R=4.55$ $b_R=4.55$ $c_R=2.86$ |                 |                 | 90°,90°,90°    |

| Monoclinic | $P2_1/c, (C_{2h}^5)$    | $a_{M1} = 5.38$                  | $b_{M1} = 4.54$ | $c_{M1} = 5.75$ | 90°,122.6°,90° |

Table 1.1: Rutile and Monoclinic phase comparison

for multi-grain sized VO<sub>2</sub>[10], or cascade for single crystal VO<sub>2</sub>[5]. Although the hysteresis is not favored for application, there is no good method can suppress the hysteresis effectively.

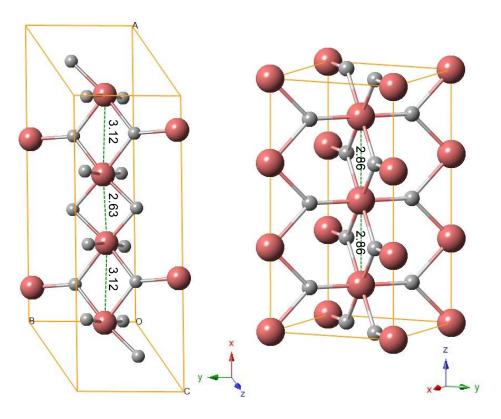

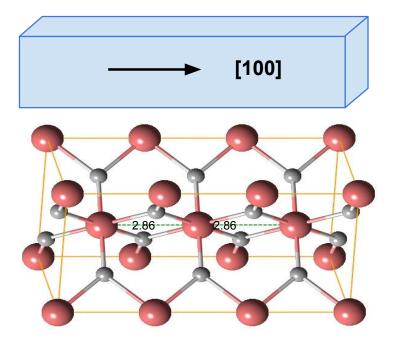

1.3.1 Physical and electronic structure of VO<sub>2</sub>

The phase transition is a first order transition. When temperature belows  $T_c(340K)$ ,  $VO_2$  is in monoclinic (P2<sub>1</sub>/c) phase. The characteristics of this phase is the  $V^{4+}$ - $V^{4+}$  pairs in c axis have alternate separations of 2.63Å and 3.12 Å as shown in left of Figure 1.5. Compared with the rutile metal phase when temperature is higher than  $T_c$ , the  $V^{4+}$ - $V^{4+}$  pairs has a fixed separation of 2.86Å. The structural difference causes the number of  $V^{4+}$  in unit cell doubled from metal phase to insulator phase. However, since the monoclinic phase now has almost as twice length on c axis. This makes the experimental observable change rather smaller. In fact on single crystal  $VO_2$ , the experiments[61, 62] work has shown there is about 1% expansion from rutile phase to monoclinic phase.

Table 1.3.1 shows the lattice comparison.

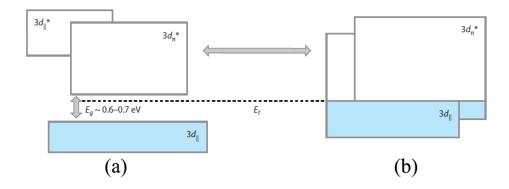

The band gap of VO<sub>2</sub> has been studied by different means, the optical studies shows: the band gap is  $0.2\sim0.3$  eV for rutile metal state; for monoclinic insulating state, optical band gap is  $0.6\sim0.7$  eV[12, 63]. The relationship between MIT and electronic structure of VO<sub>2</sub> are qualitatively explained by Goodenough in 1971[64]. In this work, he proposed the Peierls-type structurally-driven MIT model to explain the MIT behavior. The vanadium atom has electron configuration [Ar] $4s^23d^5$ , this atom bound to two oxygen atoms has the  $1s^22s^22p^4$  configuration. Four electrons of vanadium fill oxygens' shell. The Vanadium atom has a single electron left near its fermi level. The electrons in O atom form a closed shell and lie below the fermi level. Because of the anistropic crystal field. The level where the electrons reside are split into two level manifold( $e_g$ ) and three level manifold( $t_{2g}$ ). The  $t_{2g}$  state again splits into  $d_{//}$  and  $d_{\pi}$  states. The  $d_{//}$  and  $d_{\pi}$  states overlap with  $d_{//}$  filled with a single electron on the bottom. Fermi level lies in d band, which makes it rutile metal phase as shown in Figure 1.4. As for the monoclinic phase, the  $V^{4+}$ - $V^{4+}$  paring parallel to the c-axis splits the  $d_{//}$  band into bonding and antibonding states. An energy gap about  $0.6eV\sim0.7eV$  is formed between  $3d_{//}$  band and  $3d_{\pi}^*$  band in Figure 1.4 (a).

Figure 1.4:  $VO_2$  band diagram

#### 1.3.2 Mott transition vs Peierls transition

The challenging to study VO<sub>2</sub> transition is complicated by the entanglement of Mott transition vs Peierls transition(Structure transition). As discovered by Morin in 1959[10], VO<sub>2</sub> has been the focus of research. However, when VO<sub>2</sub> electronic structure changes with temperature, its structures also changes. Both transition happens about the sample temperature( 340K). There has been a long debate about which transition dominate the transport properties as well as optical properties[17, 65–69]. Recently, the synthesis of single crystal

Figure 1.5:  $VO_2$  Crystal structure: Left: Monoclinic insulating phase; right: Rutile metallic phase

$VO_2[61]$  has enabled another approach to study at  $VO_2$  metal insulator transition.

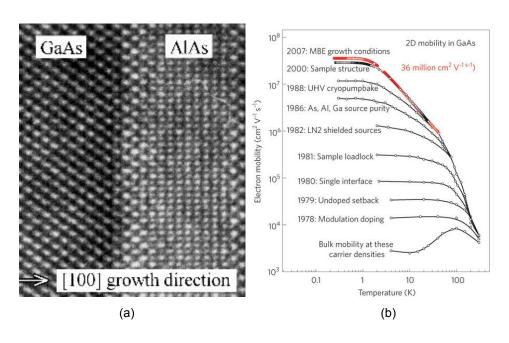

#### 1.4 GaAs introduction

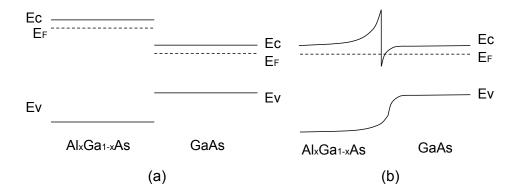

Another strongly correlated system used in this study is GaAs/AlGaAs heterostructures as shown in Figure 1.7 (a). Aluminum gallium arsenide  $(Al_xGa_{1-x}As)$  is a semiconductor nearly the same lattice constant as GaAs. It has larger bandgap than GaAs. The x in the formula above is a number between 0 and 1. This indicates an arbitrary alloy between GaAs and AlAs. The advantage of GaAs/AlGaAs heterostructures is that the mismatch of the lattice between GaAs and AlAs is very small (AlAs) lattice constant is 0.15% larger than GaAs) in Figure 1.7 (a). This allows the heterostructures formed in GaAs/AlGaAs to have very little impurity and induced strain. As a result, it has the highest electron mobility in record. The highest mobility record of GaAs/AlGaAs heterostructures is 36,000,000 cm<sup>2</sup>/Vs. [70]. To make a comparison, the highest mobility in MOSFET is roughly 80,000 cm<sup>2</sup>/Vs. The device we used in our study is confined electrons in two dimensions. Normally by tuning the dimensions of system, we expected different physical properties. For example, the magnet moments and local volume have different in various dimentions [71]. The single electron device is based on zero dimension electrons [72].

After two type of semiconductors are placed in contact to form the heterostructure, rearrangement of mobile carriers which occur near the compositional junction. As a result, electrons move from the semiconductor with the higher Fermi-level to the other, and an electric field is produced to balance this transfer. At end an equal fermi level is reached. The built in potential tilts the conduction band at the interface to have a local energy minimum, a confined quantum well is formed as illustrated in Figure 1.6. Another type of quantum well can be created by applying sandwich structure ( $Al_xGa_{1-x}As$ -GaAs- $Al_xGa_{1-x}As$ ).

Figure 1.6: Quantum well formation: two bulk material in contact. Equilibrium of Fermi level bend the conduction band

Most GaAs/AlGaAs heterostructure has a delta doping layer next to it. Delta doping supplies charge carriers, usually Carbon for P doping and Silicon for N doping. Delta doping is known to cause much less imperfection than normal doping method. However, this small sacrifice of quality becomes critical in situation to distinguish Anderson localization(disorder caused) or Wigner crystallization(interaction caused). To achieve almost no imperfection is to grow undoped GaAs/AlGaAs heterostructures. For this type of structure, there is no intrinsic dopant. Carriers are only capacitively induced by a metal gate, and the carrier density is controlled by the gate voltage. This is the concept of a HIGFET illustrated in details in Chapter 6.

Figure 1.7: a) GaAsAlGaAs interface TEM pictures. b)Mobility improvement of GaAs.[2]

#### **CHAPTER 2 Fabrication**

#### 2.1 Basic of fabrication

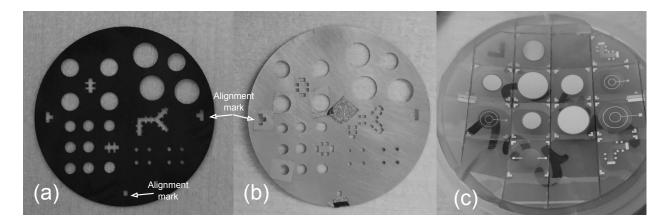

#### 2.1.1 Shadow method

Shadow masking is a simple technique. The masks we have designed are 1 inch diameter circular stainless steel sheet. The patterns are created by intense laser burning. This method usually has been used in large sample and making contacts to it. This method is usually used in making thin film like sample. The masks are in pair. One mask for growing sample (Figure 2.1 a), the other mask for making contacts (Figure 2.1 b). Mask shown in Figure 2.1 a is used to attach to the substrate wafer, the sample material will be evaporated on to the substrate through the opening on mask. When the growth is done, the substrate has the thin film in the shape shown in Figure 2.1 a. Next step, mask in Figure 2.1 b is used. Three small patterns on the rim serves as the alignment mark. The masks and wafer need to be well aligned to guarantee the location of the contacts on right position. The contacts are made by thermally depositing metals (We use Au/Cr.). The contacts deposition will form the same shape as the pattern in Figure 2.1 b. This method has been used to make VO<sub>2</sub> polycrystalline sample on SiO<sub>2</sub> substrate. Figure 2.1 c shows a finished 1 inch wafer with various patterns on it.

# 2.1.2 photolithography

Photo-lithography is the first step in nano-fabrication. All the modern computer chips are manufactured by Photo-lithography. In industry, the Extreme Ultraviolet Lithography (EUV) is used to make the fabrication resolution approaching 10 nm [73]. At Wayne state university, our lithography equipment (MJB-3) has a resolution of  $0.6 \mu \text{m}$ . Most times the resolution we can approach is also limited by the microscope on MJB-3. Consider all these

Figure 2.1: a) Shadow mask for sample thin film deposition. b) Shadow mask for metal contacts deposition. c) Finished sample with contacts on it.

factors, we have an estimated accuracy of 2  $\mu$ m aligning the pattern. Below are several steps for the photo-lithography, the schematic diagram is illustrated in Figure 2.10:

#### 2.1.3 Clean room environment

Our devices are all fabricated in a class 100 cleanroom in physics department at Wayne state university. The temperature and humidity are well controlled in desired range by airtech system. The temperature in our clean room is  $68\pm2^{\circ}F$ . The humidity is controlled  $48\pm3\%$ . The condition is crucial for the success of fabrication.

#### 2.2 Fabrication on GaAs device

The GaAs wafer used in our lab are provided by our collaborators from Princeton University and Sandia National Laboratories. The wafers are made with well defined layered structures form GaAs-AlGaAs quantum well(See Figure 2.3). The works we did in Wayne state university include making the raw wafer into different electronic device for various measuring purpose.

The fabrication includes the following major steps:Lithography, Etching, Metal deposition, Making Ohmic contacts. Following illustrates these steps.

Figure 2.2: Clean room environment

## 2.2.1 Lithography

The purpose of lithography is to make a thin film  $(1\sim2~\mu\text{m})$  material with certain patterns. The opening on the pattern exposes the sample surface. This part of the sample can be etched away and deposit metal to make Ohmic contacts.

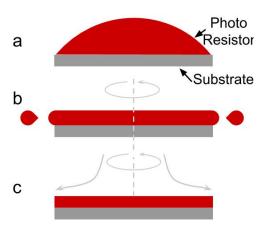

## **Spincoat**

Spin coating is a common techniques for applying thin films to substrates. It is widely used in industries and research. It can quickly and easily produce uniform films, the thickness ranging from a few nanometres to a few microns. In our fabrication, firstly, spin coat the sample with photo-resistor. The photo resistor is dropped on sample which form a dome shape in Figrure 2.4 a. Then the substrate is rotated at high speed on spinner and the most of photo resistor fly off the substrate(Figure 2.4 b). For a large wafer spin coating, the air is blowing from top on to the photo resistor. In our lab, we don't apply air flow since the samples we use have a small size( $<1\text{cm}^2$ ). After spin, the photo resistor left on substrate forms an uniformly thin film. The photo resistors we commonly used in our clean room are AZ4620 and Shipley S1811/S1813. Both are negative photoresistor. The spin speed-thickness relation can be found in photoresistor data sheet. A good estimation can be done using  $t \propto \frac{1}{\sqrt{\omega}}$ . We normal use a thickness larger than  $1\mu$ m photoresistor.

#### Soft-bake

After spin-coated, the photoresistor need to be soft-baked before using. Solvents can be removed during Soft Baking. The photoresistor becomes photosensitive only after softbaking. The baking time and temperature varies with photoresistor type. See the Table 2.1 for soft bake details. The soft baking temperature and time need to be well controlled. Over

Figure 2.4: Spin coat substrate with photo resistor

baking can degrade the photosensitivity of photoresistor. Under baking can prevent UV light during the exposure procedure. If the sample has been soft-baked but left in a high moisture environment for a long time, it is necessary to soft bake it again.

| Photoresistor | bake type | temperature( ${}^{\circ}C$ ) | time(s) |

|---------------|-----------|------------------------------|---------|

| AZ4620        | soft      | 95                           | 95      |

| AZ4620        | hard      | 105~110                      | 180~300 |

| S1811         | soft      | 115                          | 60      |

| S1813         | soft      | 115                          | 60      |

Table 2.1: Table to test captions and labels

#### Expose pattern

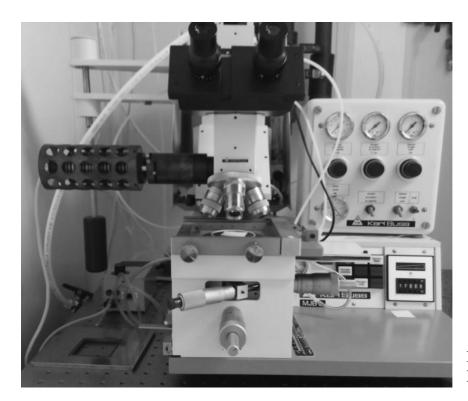

To expose pattern, we use Karl Suss MJB3 mask Aligner to align the pattern on the mask to the sample. After alignment, a 365nm UV light is uniformly exposed to the sample. The expose time can be derived from formula:  $\frac{Dose}{UVintensity}$  The photoresistor specific required dose can be found from the photoresistor data sheet. The typical exposure time used in our samples is ranging from 15 to 27s.

#### Development

After exposure, the sample can be developed using developer. The developer used for GaAs is AZ400K diluted with DI H<sub>2</sub>O at ratio 1:5. The development time can be found in

Figure 2.5: Karl Suss MJB3 MASK ALIGNER

photoreisitor data sheet. To develop the photoresistor, the exposed sample is immersed into a baker with developer. To have a rough estimated develop time for large patterns(visible). We develop until exposed pattern become clear and wait for extra 5s before immerse into DI water.

## Hard-Bake(post expose bake)

The hard-bake is used to harden the resist image after development. Similar to soft-baking, during this step sample will be put on surface of hotplate. This step will make photoresistor withstand the harsh environments of etching. Usually high temperatures are used (100C - 120C). Such high temperature will crosslink the resin polymer in photoresistor. By doing this, the photoresistor image becomes more thermally stable. Hard-bake also helps to improve photoresistor adhesion to the wafer surface. The only photoresistor we have been used for hard-bake is AZ series. The temperature and baking time is shown in Table 2.1.

# **Etching**

Etching on GaAs devices are all done by using wet etching. The enchant are made of  $H_2O_2$ ,  $H_2SO_4$ ,  $H_2O$  in a ratio of 4:5:16. Two type of etching condition has been used in this thesis:

Etching in the light: Etching in the light is more generally used define a hall bar pattern on the sample. For p-doped sample, photoresistor protect the hall bar pattern, the rest will be etched away by using etching in the light, leave buffer substrate. For undoped HIGFET sample, the light etching will etch away the area except the gate region.

Etching in the dark: Dark etching is only used for HIGFET contacts etching in this work. As shown in Figure 2.6, the dark etching has a slight low etch rate(8.66 nm/s) than light etching rate(8.99 nm/s). However, the profile of dark etching are different from light etching.

Figure 2.6: Etching rate at different conditions (Room temperature at  $69.2^{\circ}F$ , humidity at 47%)

Figure 2.7: Etching profile observed by using SEM

## 2.2.2 Metal deposition

# Thermal evaporation of metal

Deposition of metal can make ohmic contact to the sample. The developed sample has photoresitor patterns. These patterns has opening like windows allow the evaporated metal to go through. Sample is anchored to a round metal plate inside vacuum chamber (Figure 2.8 a). This plate can rotate and tilt to a certain angle. Metal source is heated with a large current to evaporate. During the evaporation, the thickness of deposition is recorded by a film thickness monitor down to 1Å. The depositing instrument we used in our lab is nano 36, with powerful turbo pump it can quickly pump down to 3E-8 torr. This level of high vacuum is helpful for making a good deposition. Also, a good vacuum can prevent the metal from oxidization during the evaporation. During each deposition, the chamber pressure of Nano 36 is under 2E-6 torr. There are two type of metal deposition. The contact metal and gate metal deposition. Deposition recipes are listed in Table 2.2.

#### Liftoff

Liftoff is the last step in lithography. Finally, after the deposition is done, the sample

Figure 2.8: Kurt Lesker Nano36 deposition system platform

| Device | type    | material 1 | thickness(nm) | material 2 | thickness(nm) |

|--------|---------|------------|---------------|------------|---------------|

| p-GaAs | contact | AuBe       | 95            | Au         | 5             |

| p-GaAs | gate    | Cr         | 30            | Au         | 15            |

| HIGFET | contact | AuBe       | 160           | Au         | 10            |

| HIGFET | gate    | Cr         | 30            | Au         | 15            |

| n-GaAs | contact | AuGe       | 70            | Au         | 5             |

| n-GaAs | gate    | Cr         | 30            | Au         | 15            |

Table 2.2: Table of metal deposition

will be soaked into acetone to remove the photoresistor. There are a few factors can effect the liftoff, which need to be considered. The first thing is the exposed pattern need a good undercut wall to guarantee the liftoff. The idea of under cut is shown in Figure.2.9. This corresponds to the develop step in Figure.2.10. If the under cut is not good enough, the deposited metal can connect as one whole piece, and acetone wont go though the metal to clean the photoresistor. Secondly, the surface has to be kept as clean as possible. If there are dust or small dots on the surface. They can pin the photoresistor when during liftoff. Lastly, The metal deposition has to be done in a sufficient low pressure, otherwise, the thermal

evaporated metal particles can carbonize the photoresistor.

Figure 2.9: Undercut walls(right) vs no undercut wall(left), The black color is substrate, the blue color is photoresistor

Figure 2.10: Major photo lighography procedures

## 2.2.3 Making Ohmic contact

The Ohmic contacts are important for a working electronic devices. To make an ohmic contact. After lift off, the device will be put into forming gas and annealed at high temperature to overcome the Schottky barrier.

For p-doped GaAs device sample, annealing has been done at  $485^{\circ}F$  for 10 minutes. The chamber has been preconditioned with flushing forming gas. The forming gas used in our

Figure 2.11: Anti-Hall bar sample fabrication

lab is  $5\%H_2+95\%N_2$ . When sample surface temperature reached  $485^{\circ}F$ , the forming gas stops flushing and the chamber pressure stays around 350 mbar.

### 2.2.4 Three types of GaAs sample

# Anti hall bar sample

Figure 2.11 shows the anti hall bar sample fabrication. The p-doped GaAs sample is photolighography with light green pattern in Figure 2.11 a. Then elsewhere is etched down below 2D hole layers (About 500 nm for p-type GaAs sample used in this work). After etching, only the square-donut part has a 2D hole layers, elsewhere is left with semi-insulating GaAs bulk substrate layer (Figure 2.3). After this square donut, another lithography need to open 12 windows on the metal contacts area shown in Figure 2.11 b. The mask is used has to be in pair with the first mask. The patterns are self alighed through the alignment mark. Finally the contacts need to be annealed with forming gas at certain temperature to form ohmic contacts.

## GaAs HIGFET sample

HIGFET stands for Heterostructure Isolated Gate Field Effect Transistor. In this work, HIGFET is GaAsAlGaAs without doping. Unlike doped GaAs material, HIGFET has no

Figure 2.12: GaAs HIGFET sample fabrication

intensional doping, all the carriers comes from field effect. The HIGFET sample has a heavily doped layer on surface which is grown by MBE. This heavily doped layer serves as the top gate. To fabricate HIGFET, we firstly make a standard Hall bar using photolithography. Then the Hall bar area is protected and elsewhere is etched down, the etching depth depends on the sample structure. After etching, the sample is shown in Figure 2.12 a. This step will guarantee only the Hall har area has the 2D interface. The following step is depositing metal contacts and annealing. The metal thickness, annealing time and temperature are tricky parameters which need to be fine tuned to obtain a functioning device. Details about this step is discussed in Chapter 6. After contacts have been made, the final step is depositing metal to the gate. Since the same itself has a heavily doped layer, we only need to deposit metal to the surface. Note this step is not deposting the gate, depositing two square as shown in Figure 2.12 c can prevent surface oxidation as well as making it easier for wiring.

### Gated p-type GaAs sample

The gated p-type GaAs sample is a standard hall bar measurement setup with a metal top gate. To fabricate this type of sample, metal contacts are firstly deposited on surface of GaAs. Contacts are annealed at 485°C for 10 minutes to form ohmic contacts. Secondly,

a top metal gate is deposited in the center of the sample. The position of metal gate is controlled by alignment mark. Then, another lithography is used to make a layer of photoresistor to protect the area connecting metal contacts and metal gate. Lastly, etching removes the the uncovered area. Both photoresistor protected and metal protected area will stay. The p-doped GaAs sample we used in our research has no heavily doped surface layer. In another words, the metal gate defines the 2D carrier area. The gate has to be made before etching away the unprotected material so that the 2D carrier is well covered by metal gate. This way reduces the gap or any misalignment between top gate and 2D layer. The contacts have to be produced before top gate, otherwise, annealing contacts will short the top gate to 2D layer.

Figure 2.13: Gated p-GaAs sample fabrication

# 2.3 Fabrication on $VO_2$ device

There VO<sub>2</sub> devices in this work include VO<sub>2</sub> film based and VO<sub>2</sub> nanobeam based. For VO<sub>2</sub> film, making a device is not difficult. Even without lithography, putting silver paint on VO<sub>2</sub> film yields good contacts. This section focus on the fabrication of VO<sub>2</sub> single crystal nanobeams.

# 2.3.1 Polycrystalline VO<sub>2</sub> preparation

Vanadium dioxide thin film can be synthesized from metal-organic chemical vapor deposition method[74], physical vapor deposition[75], pulsed laser deposition(PLD), sputtering and sol-gel[76–78].

In this thesis, VO2<sub>2</sub>thin film was deposited through pulsed laser deposition on the SiO<sub>2</sub> thin layer. Our thin film VO<sub>2</sub> sample is from Dr. Nelson Sepúlveda's group in Michigan State University. As shown in Figure 2.14, the substrate was placed into a vacuum chamber with oxygen gas pressure at 20 mTorr. A metallic vanadium target was ablated using a KrF excimer laser was ablated by excimer laser pulses with energy of 352 mJ per pulse (fluence of  $\sim 2 \text{ J/cm}^2$ ) and a frequency of 10 Hz. A ceramic heater used to heat the sample was maintained at 595 °C through 25 min deposition. Following the deposition, 30 min annealing process was performed with the same deposition conditions [79]. The single crystal nanobeam of VO<sub>2</sub> in this thesis is synthesised by physical vapor deposition[5]. The schematic for physical vapor deposition is Figure 2.15, V<sub>2</sub>O<sub>5</sub> powder source is placed in a ceramic boat located in the center of a tube furnace setup, and a silicon substrate with SiO<sub>2</sub> covered surface is placed  $3 \sim 5$ cm away from the edge of the boat in the downstream direction. Argon flows into the tube at a constant rate as a carrier gas, and a mechanical pump maintains the tube in vacuum. Then, the furnace temperature is ramped to  $900 \sim 950^{\circ}$ C in 30 min, and is maintained for 30 min before cooling down naturally. The flow parameter has to be controlled to make single crystal VO<sub>2</sub> nanobeam. The thickness and width of nanobeam are usually from 40 nm to 2  $\mu$ m. The length can goes up to hundreds microns.

Figure 2.14: Schematic of Pulsed laser deposition of Polycrystalline VO<sub>2</sub>

# 2.3.2 Single crystal VO<sub>2</sub> preparation

Our single crystal VO<sub>2</sub> nano beam is provided by our collaborator from Dr. Jie Yao's research group at the University of California, Berkeley and Jiwei Hou from Tsinghua university at Beijing. Vanadium dioxide single crystal nano beam are grown at a rather high temperature 900-1100°C[5]. Although this temperature is lower than melting point of  $SiO_2(1600^{\circ}C)$ , this temperature soften SiO2 substrate and embedded VO<sub>2</sub> into the SiO<sub>2</sub>, which results in a large strain along the c-axis. This external strain cause the transition temperature much higher and the transition is not sharp. To reduce this strain effect. Buffered oxide etch(BOE) is used to etch a very thin  $SiO_2$  layer. After the  $SiO_2$  around  $VO_2$  nanobeam is reduced, some  $VO_2$  nanobeams then become loosely bonded to the substrate and therefore can be transferred on to another  $SiO_2$  substrate using micro-manipulator.

Figure 2.15: VO<sub>2</sub> single crystal nanobeam synthesis diagram

The transferred sample has adhesion with the new substrate. Compared with the original substrate where the VO<sub>2</sub> nanobeams grown, the strain are much less. As shown in Chapter 5, the transition are rather different.

# 2.3.3 Sample transfer

The VO<sub>2</sub> single crystal nanobeam has a grown temperature 900  $\sim 950^{\circ}$ C. This condition makes the VO<sub>2</sub> single crystal nanobeam embedded in the substrate and has a large strain comes from the substrate. A few works[5, 61, 80] has demonstrated that embedded VO<sub>2</sub> single crystal nanobeam has a "poor" transition behavior. To avoid this, we have to transfer the sample from original substrate to a new substrate. By doing this, the strain will be greatly reduced. All our measurement on single crystal VO<sub>2</sub> nanobeam are based on the transferred sample. The Figure 2.17 compared the sample before and after transfer. To transfer the sample, we used PC pick up method.

### 2.3.4 Lithography

The lithography on VO<sub>2</sub> can only been done by using developer MF319, the developer AZ400K for GaAs will react with VO<sub>2</sub>. To work with MF319 developer, we choose

Figure 2.16: Embedded  $\mathrm{VO}_2$  nanobeam vs Strain free  $\mathrm{VO}_2$  nanobeam

S1811/S1813 as our photoresistor for masking. The thickness of VO<sub>2</sub> nanobeam can ranges from 20nm up to  $2\mu$ m[30]. In our work, most tested VO<sub>2</sub> nanobeam are chosen to be around 1  $\mu$ m. Wth this, we need a thicker photoresistor by using slower spin speed. Then soft bake at temperature according to Table 2.1. The following procedures are standard includes: exposure contacts with UV, develop the photoresistor, thermally deposit metal contacts, liftoff.

Figure 2.17:  $VO_2$  capacitance sample: a) Thin film  $VO_2$  on Si substrate, the p-doped substrate serves as bottom gate. b) Single crystal  $VO_2$  with top gate and bottom gate.

Another thing to note is depends on the sample surface cleanness, the liftoff are different.

The cleaner the sample surface started with, the easier and better liftoff will be. For those sample surface is not perfect, metal deposition need thinner to ensure the success of liftoff.

# CHAPTER 3 Measurement techniques

# 3.1 Transport measurement

## 3.1.1 Ohmic contact

After fabrication, next step needs to check if the sample's contacts are Ohmic. When you create a junction between a metal and a semiconductor, some interesting things can happen. The Schottky barrier forms in between the interface, and it may stops the charge carriers to flow easily.

Figure 3.1: (a) Schottky barrier forms between metal insulator junction with a height of  $\Phi_B$ . (b) Ohmic contact I-V curve(orange) vs non-Ohmic contact I-V curve(blue).

One simple way to test if the juction is ohmic is to measure its I-V characteristics. As shown in Figure 3.1(b), Ohmic contacts shows linear I-V dependence. When it is non-Ohmic, the I-V dependence is non linear. Another way to check if the sample contacts are Ohmic is to compare the resistivity from four terminal measurement and two terminal measurement. Suppose we have four terminal on sample, if two terminal measurement and four terminal

measurement shows same level of resistivity, the contacts are Ohmic. If the two terminal resistivity is much higher, the contacts are normal not ohmic. The validity is illustrated in section below. One advantage of using this method is to protect the sample. Some of our sample are fragile to electrical current. We limit our current to 1nA for protecting these samples. With this small excitation, comparing four terminal and two terminal AC resistivity is more feasible.

#### 3.1.2 Four terminal and two terminal measurement

The mostly used measurement techniques in this thesis is four terminal measurement as shown in Figure 3.2 a, where a current is driven between opposite side contacts while the voltage is measured across two adjacent corner contacts  $(V_{xx})$ . The voltage dividing the current yields resistance. Compared with four terminal measurement, two terminal measurement has a source and drain. The resistivity can be obtained using the voltage divide the current going through.

If the sample contact is not good, the two terminal measure result differs from four terminal measurement. Four terminal result is significant smaller than two terminal result. The reason is when performing four terminal measurement, suppose the contacts are bad, the current will not choose to pass though the voltage since they have a higher resistance than the sample bulk. Without current pass though, there is no voltage drop on bad voltage contact. This way the difference of voltage between two voltage reflects the real voltage drop on the sample.

When doing two terminal measurement (Figure 3.2 b) and suppose the contacts are not ohmic. As current is running from 1 to 2, the bad contact makes voltage drop across contacts it self. Then the measured voltage from voltage meter does not reflect the real voltage drop

Figure 3.2: Four terminal measurement setup

across the sample.

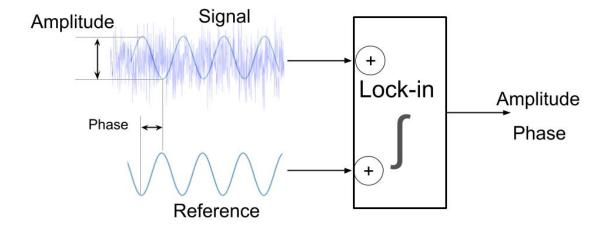

### 3.1.3 AC Lock-in amplifier

Lock-in amplifier is a commonly used in transport measurement. It can detect a small signal among tons of noise. Depending on the setup, the lock-in can measure a signal when the noise level is  $10^6$  times larger than signal level. The principle of lock-in comes from orthogonality of sinusoidal functions.

Assume the noises have signals at frequency  $f_i$ , the real signal  $f_1$  together with other  $f_i$  multiplied by reference sinusoidal function of frequency  $f_1$  and integrated over a time much longer than the period of the two functions, except  $f_1$  signal, the rest frequencies signals result in zero. Noise is eliminated in this way.

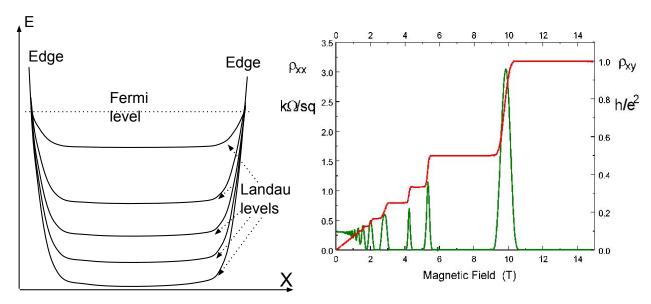

### 3.1.4 Quantum hall measurement

Quantum hall effect has been discovered in 1971. A detailed description of quantum hall effect can be found in book by Stone[81]. The main idea is: when sweeping magnetic field, the Fermi energy will be tuned through different Landau levels. This makes longitudinal resistivity stays 0 at most time except when the Fermi energy is crossing one Landau level,

Figure 3.3: Lock-in amplifier

the longitudinal resistivity reflects the bulk behavior. As for the Hall resistivity, it equals to the number of Landau levels lower than the Fermi level times the quantum resistance. It equals to the number of edge channels.

Figure 3.4: Left:Landau levels and fermi energy in a quantum hall system. Right, the longitudinal resistivity and Hall resistivity as function of magnetic field in integer quantum hall effect

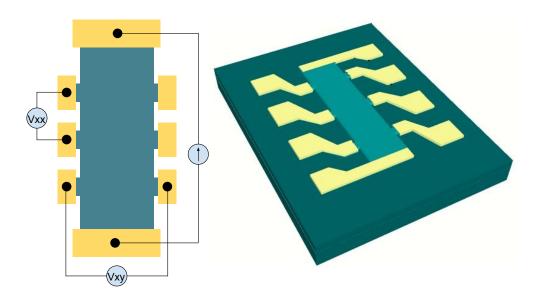

The standard setup to do a quantum hall measurement is called Hall bar in Figure 3.5.

The current is uniformly applied through the source and drain leads. The longitudinal

resistivity which is the green peaks in Figure 3.4 is measured by monitoring  $V_{xx}$  in Figure 3.5. The hall resistivity which is the red plateau in Figure 3.4 is measured by monitoring  $V_{xy}$  in Figure 3.5.

When magnetic field is applied, left edge and right edge are both dissipation state, this point, there is no state where the carriers can scatter into, so it appears the same potential on each side. For understand the hall resistivity plateau, suppose the magnetic field is coming out of page in Figure 3.5, electric field is supplied from bottom current lead to top. The Lorentz force makes carriers turns in a way which obey right hand rule. We can easily figure out that the right voltage contacts has the same potential as bottom lead and left has same as top. The conductance between them is through the quantized edge channels. It starts with a lot of edge channels at low magnetic field. As magnetic field increases, Landau levels spacing increases, which led to less edge channels cross Fermi level at edge. As we can see in Figure 3.4, after 11T, the  $\rho_{xy}$  reaches  $h/e^2$ . The resistivity value  $h/e^2$  is called resistance quantum which is about 25813 $\Omega$ . One resistance quantum means there is one channel for charge carriers at the edge.

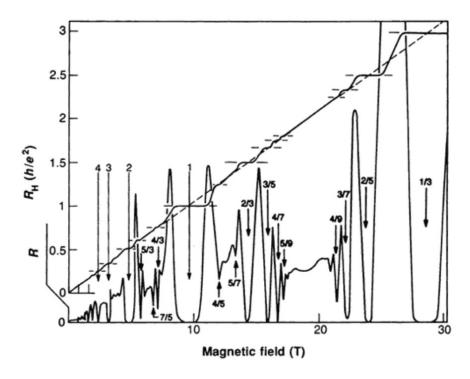

This is the integer quantum hall effect. It can be well understood with the framework of Landau energy splitting and edge channel conducting. An interesting question comes, what will happen if we increase the magnetic field after the hall resistivity already reaches  $h/e^2$ ?

It turns out into another interesting yet not well understood phenomena which is known as fractional quantum hall effect. Where the number of edge channels turns out to be not integer! As shown in Figure 3.6, there could be 1/3 of channel conducting! What happened? To understand the fractional quantum hall effect, again, we have to consider the correction effect. It is caused by electron-electron interaction together with magnetic flux

Figure 3.5: Quantum Hall measurement schematic

which forms into composite fermions. This is still not a completely understood area and a lot of active research is still going on. It attracts fundamental research as well as applications. For example, 5/2 state which is known to obey non-abelian particle statistics, is a promising candidate to pave the way to realizing an experimental platform for quantum computing[82]. Details of fractional quantum hall effect is out of the scope of this thesis work. The this work uses integer quantum hall effect to characterize the 2D carriers as well as to drive the carriers into a strong interacting state.

## 3.2 Low temperature

There are a few cryogenic systems used in this study: Leiden He3/He4 dilution refrigerator; Quantum design PPMS system; Lakeshore flow cryostat. The PPMS system and flow cryostat can goes down to near 3K, which is good to use for pretest sample. Flow cryostat can also be used for high temperature. The dilution refrigerator is used to achieve a temperature of mK range. At which temperature we can measure intrinsic transport behavior of electrons.

Figure 3.6: Fractional Quantum Hall effect.[3]

# 3.2.1 He3/He4 dilution refrigerator

The Figure 3.7 shows a dry dilution re-fridge system. The system is pre-cooled to 3K with a pulse tube. It takes 2 days to cool down to 3K. This procedure doesn't cost any Helium loss. Then circulation of He3/He4 mixture can cool the lowest plate to 5mK. As shown in Figure 3.7, it is a complicated system with different stages at fixed temperature. The system also has a superconducting magnet on the bottom. The sample is inserted from the top of the fridge. The inserting need to be slow to avoid sudden temperature jump on the sample. Sample has to stay at each temperature stages until fully thermalized before lowing to next stage. The sample measured at mK temperature allow us to do a transport measurement. In quantum hall measurement, the magnetoresistance  $(\rho_{xx})$  and Hall resistance  $(\rho_{xy})$  is measured at a low frequency less than 20Hz. To avoid noise, low pass filter are built on each single line on the probe.

Figure 3.7: Structure of inset of dilution refrigerator with different cooling stage